# **LOONGSON**

# Instruction manual of Loongson 3A4000 processor register

Multi-core processor architecture, register description and System Software Programming Guide V1.5

Loongson Zhongke Technology Co. LTD

#### Copyright statement

The copyright of this document belongs to Loongson Technology Co., LTD., and all rights are reserved. No company or individual may publish, reprint or otherwise distribute any part of this document to third parties without written permission. Otherwise, it will be held legally liable.

#### disclaimer

This document only provides phased information. The contents can be updated according to the actual situation of the product at any time without prior notice. The Company shall not be liable for any direct or indirect losses caused by improper use of documents.

#### Loongson Zhongke Technology Co. LTD

Loongson Technology Corporation Limited

Address: Building 2, Loongson Industrial Park, Zhongguancun Environmental Protection Technology Demonstration Park, Haidian District, Beijing

Building No.2, Loongson Industrial Park,

Zhongguancun Environmental Protection Park, Haidian District, Beijing

Tel: 010-62546668 Fax:

010-62600826

# ----- Reading guide

The Instruction manual for The Processor Registers of Loongson 3A4000 introduces the architecture and registers of the multi-core processor of Loongson 3A4000, and gives a detailed description of the chip system architecture, functions and configurations of main modules, register lists and bit fields.

# Revision history

|                        | The document name: | Instruction manual of Loongson 3A4000 processor register |

|------------------------|--------------------|----------------------------------------------------------|

| Document update record | The version number | V1.5                                                     |

|                        | founder            | Chip R&d Department                                      |

|                        | Creation date      | 2019-12-20                                               |

# **Update history**

| The seria  | Updated<br>date | The version | Update<br>the                                                                    |

|------------|-----------------|-------------|----------------------------------------------------------------------------------|

| 1          |                 | number      | content                                                                          |

| num<br>ber |                 |             |                                                                                  |

| 1          | 2018-05-08      | V0.1        | The initial release                                                              |

| 2          | 2018-05-28      | V0.2        | Update various chip configuration registers                                      |

| 3          | 2018-06-02      | V0.3        | Add the section of frequency division control and update GPIO, UART, I2C and SPI |

| 4          | 2018-06-04      | V0.4        | Modify the routing                                                               |

| 5          | 2018-06-05      | V0.5        | Modify memory controller section to add software clock system                    |

| 6          |                 |             | Add clock description; Add GPIO interrupt description;                           |

|            | 2018-06-13      | V0.6        | Increase temperature status detection; Add HT interruption                       |

|            | <br> -          |             | description; Add 3A3000 compatibility description; Modify                        |

|            | <br> -          |             | EXTIOI to support 8-node interconnection; Modify the processor core description. |

| 7          | 2018-09-11      | V0.7        | Update the configuration register list, adding some register                     |

| ,          |                 |             | field descriptions.                                                              |

| 8          | 2018-09-13      | V0.8        | Update the stable Clock structure description.                                   |

| 9          | 2018-10-26      | V0.9        | Update the DDR section                                                           |

| 10         | 2019-02-19      | V1.0        | Internal debug version                                                           |

| 11         | 2019-05-29      | V1.1        | Update configuration register, temperature sensor, stable                        |

| 11         | 2017-03-27      | V 1.1       | Counter, extension interrupt, Scache interrupt, processor                        |

|            |                 |             | CPUCFG section description                                                       |

| 12         | 2019-07-01      | V1.2        | Some statement errors have been fixed                                            |

| 13         | 2019-09-11      | V1.3        | Chapter 4 adds part of characteristic control description                        |

|            |                 |             | 11.1.1 Fixed int_EDGE address offset                                             |

| 14         | 2019-10-11      | V1.4        | Modify the temperature sensor register description                               |

| 15         | 2019-12-17      | V1.5        | Fixed some formatting errors                                                     |

Feedback of manual information: service@loongson.cn

Problem feedback web site, http://bugs.loongnix.org/, also can be submitted to our chip production

Problems in the process of product use, and obtain technical support.

## directory

# 目录

| M | ulti-co | ore processor architecture, register description and System Software Programming Guide V1.5 | 1  |

|---|---------|---------------------------------------------------------------------------------------------|----|

|   |         | Reading guide                                                                               | 3  |

| R | evisior | n history                                                                                   | 4  |

|   | 1       | An overview of the                                                                          | 20 |

|   | 1.1     | Introduction to loong chip series processor                                                 | 20 |

|   | 1.2     | Introduction to Loongson 3A4000                                                             | 21 |

|   | 2       | System configuration and control                                                            | 24 |

|   | 2.1     | Chip operation mode                                                                         | 24 |

|   | 2.2     | Control pin description                                                                     | 25 |

|   | 3       | Physical address space distribution                                                         | 27 |

|   | 3.1     | Physical address space distribution between nodes                                           | 27 |

|   | 3.2     | Physical address space distribution within nodes                                            | 28 |

|   | 3.3     | Address routing distribution and configuration                                              | 30 |

|   | 4       | Chip configuration register.                                                                | 38 |

|   | Versi   | ion 4.1 Register (0x0000)                                                                   | 38 |

|   | 4.2 C   | Thip Feature Register (0x0008)                                                              | 38 |

|   | 4.3 M   | Manufacturer name (0x0010)                                                                  | 39 |

|   | 4.4 C   | Ship Name (0x0020)                                                                          | 40 |

|   | 4.5     | Function Setting register (0x0180)                                                          | 40 |

|   | 4.6     | Pin Drive Setup register (0x0188)                                                           | 42 |

|   | 4.7     | Functional Sampling register (0x0190)                                                       | 42 |

|   | 4.8     | Temperature sampling register (0x0198)                                                      | 42 |

|   | 4.9     | Bias configuration register (0x01A0)                                                        | 43 |

|   | 4.10    | Frequency configuration register (0x01B0)                                                   | 44 |

|   | 4.11    | Processor core frequency division setting register (0x01D0)                                 | 46 |

|   | 4.12    | Processor core reset Control Register (0x01D8)                                              | 48 |

|   | 4.13    | Route Setup register (0x0400)                                                               | 48 |

|   | 4.14    | Other Functions Set register (0x0420)                                                       | 49 |

|   | 4.15    | Celsius temperature register (0x0428)                                                       | 50 |

| 4.16 | SRAM Adjustment register (0x0430)                      | 50  |

|------|--------------------------------------------------------|-----|

| 4.17 | FUSE0 Observation register (0x0460)                    | 51  |

| 4.18 | FUSE1 Observation register (0x0470)                    | 52  |

| 5    | Chip clock frequency division and enable control       | 53  |

| 5.1  | Chip module clock introduction                         | 53  |

| 5.2  | Processor core frequency division and enabling control | 54  |

| 5.3  | Node clock frequency division and enabling control     | 57  |

| 5.4  | HT controller frequency division and enabling control  | 60  |

| 5.5  | Stable Counter split frequency and enable control      | 61  |

| 6    | Software clock system                                  | 63  |

| 6.1  | Stable Counter                                         | 63  |

| 6.1  | 1.1 Configuration address of Stable Timer              | 63  |

| 6.2  | The Node Counter                                       | 67  |

| 6.3  | Summary of clock system                                | 68  |

| 7    | GPIO control                                           | 69  |

| 7.1  | Output enable register (0x0500)                        | 69  |

| 7.2  | Input and Output register (0x0508)                     | 69  |

| 7.3  | Interrupt Control register (0x0510)                    | 69  |

| 7.4  | GPIO pin function multiplexing table                   | 71  |

| 7.5  | GPIO interrupt control                                 | 72  |

| 8    | GS464V processor core                                  | 74  |

| 8.1  | 3A4000 implements instruction set features             | 75  |

| 8.2  | 3A4000 configuration status register access            | 79  |

| 9    | Shared Cache (SCache)                                  | 81  |

| 10   | Interrupt communication between processor cores        | 85  |

| 10.1 | Access mode by address                                 | 85  |

| 10.2 | Configure register instruction access                  | 87  |

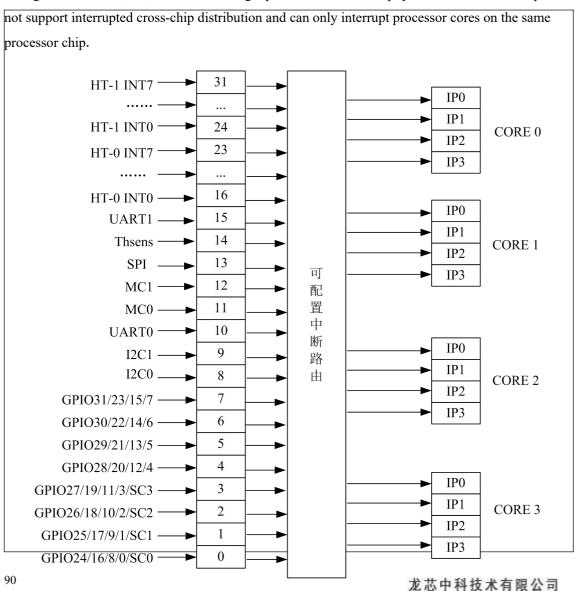

| 11   | I/O interrupt                                          | 90  |

| 11.1 | Traditional I/O interrupt                              | 90  |

| 11.2 | Extend I/O interrupt                                   | 95  |

| 12   | Temperature sensor                                     | 103 |

| 12.1 | Real-time temperature sampling                         | 103 |

| 12.2 | High and low temperature interrupt triggers.           | 104 |

| 12 3 | High temperature automatic frequency reduction setting | 106 |

| 12.4 | Temperature status detection and control.                 | 107 |

|------|-----------------------------------------------------------|-----|

| 12.5 | Temperature sensor control                                | 109 |

| 13   | Ddr3/4 SDRAM controller configuration                     | 111 |

| 13.1 | Ddr3/4 SDRAM controller features Overview                 | 111 |

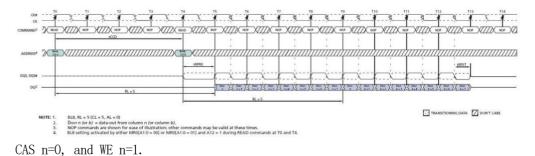

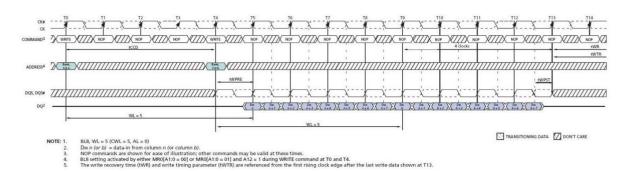

| 13.2 | Ddr3/4 SDRAM read operation protocol                      | 112 |

| 13.3 | Ddr3/4 SDRAM write operation protocol.                    | 113 |

| 13.4 | Ddr3/4 SDRAM parameter configuration format               | 114 |

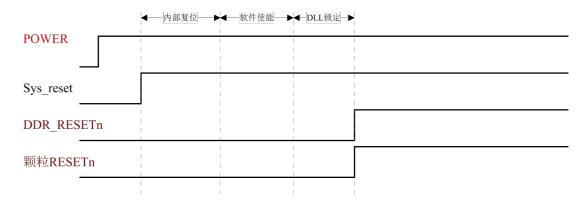

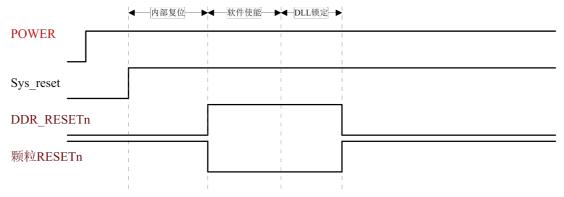

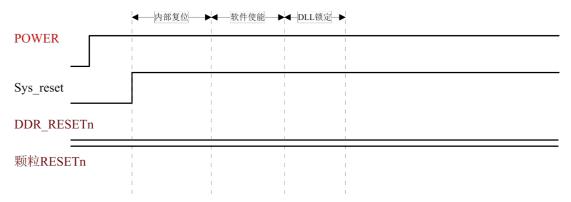

| 13.5 | Software Programming Guide                                | 128 |

| 14   | HyperTransport controller                                 | 140 |

| 14.1 | HyperTransport hardware setup and initialization          | 140 |

| 14.2 | HyperTransport protocol support                           | 144 |

| 14.3 | HyperTransport interrupt support                          | 146 |

| 14.4 | HyperTransport address window                             | 148 |

| 14.5 | Configuration register                                    | 151 |

| 14.6 | The HyperTransport bus concodes access methods for Spaces | 211 |

| 14.7 | HyperTransport multiprocessor support                     | 213 |

| 15   | Low speed IO controller configuration                     | 218 |

| 15.1 | UART controller                                           | 218 |

| 15.2 | SPI controller                                            | 157 |

| 15.3 | I2C controller                                            | 167 |

| 16   | 3A3000 kernel compatibility                               | 169 |

| 16.1 | Compatible with 3A3000 kernel                             | 169 |

| 16.2 | New feature support                                       | 172 |

| 16.3 | Configure register instruction debugging support          | 175 |

## Figure orders to record

| Figure 1-1 System Structure 1 of Loongson 3                                   |

|-------------------------------------------------------------------------------|

| FIG. 1-2 Structure of No3 of The Loong Chip 2                                 |

| Figure 1-3 Structure of Loongson 3A4000 Chip 3                                |

| Figure 6-1 Stable reset control 35 for multi-chip interconnection.            |

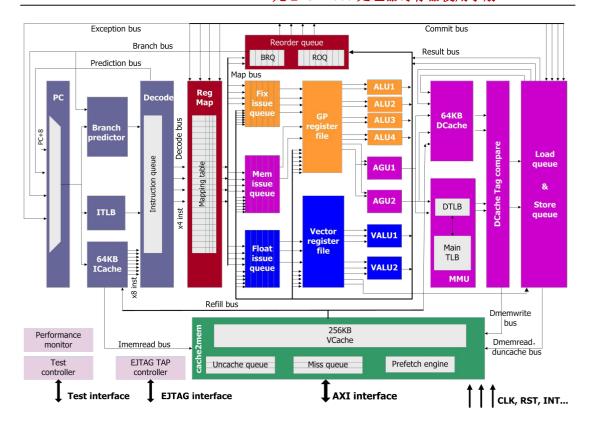

| Figure 8-1 GS464V Structure Figure 42                                         |

| FIG. 11-1 Schematic diagram of interrupt routing for longson 3A4000 processor |

| Figure 13- 1 DDR3 SDRAM read operation protocol 70                            |

| Figure 13- 2 DDR3 SDRAM write protocol 71                                     |

| Figure 14-1 Configuration access of HT protocol in Longson 3A4000             |

| FIG. 14-2 Four-chip Longshon No. 3 interconnection structure 144              |

| FIG. 14-3 Eight-chip Longshon No.3 Interconnection structure 144.             |

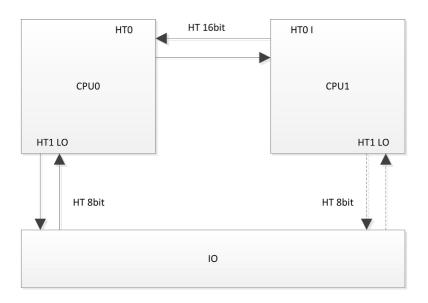

| Figure 14-4 Two-chip Longson no. 3 8-bit interconnection Structure 145        |

| Figure 14-5 Two-chip Longshop No. 3 16-bit interconnection structure 146      |

### Table item record

| Table | 2-1  | Control pin description 5                                             |

|-------|------|-----------------------------------------------------------------------|

| Table | 3-1  | Global address distribution of the system at node level $7$ .         |

| Table | 3-2  | Address distribution in nodes 8                                       |

| Table | 3-3  | SCID_SEL address bit setting 8                                        |

| Table | 3-4  | physical address distribution of 44 bits in node 8                    |

| Table | 3-5  | MMAP field corresponding to the space access property 9               |

| Table | 3-6  | Address window register Table 9                                       |

| Table | 3-7  | Correspondence between the slave device number and the module 15      |

| Table | 3-8  | MMAP field corresponding to the space access property 15              |

| Table | 4-1  | register 17                                                           |

| Table | 4-2  | Chip feature register 17                                              |

| Table | 4-3  | Manufacturer name register 18                                         |

| Table | 4-4  | Chip name register 18                                                 |

| Table | 4-5  | Function Settings register 18                                         |

| Table | 4-6  | Pin drive setup register 19                                           |

| Table | 4-7  | Functional Sampling register 19                                       |

| Table | 4-8  | Temperature sampling register 19                                      |

| Table | 4-9  | Bias setting register 20                                              |

| Table | 4-10 | Clock software frequency doubling set register 21                     |

| Table | 4-1] | Memory clock software frequency doubling set register 21.             |

| Table | 4-12 | 2 Processor core software frequency division setting register 22      |

| Table | 4-13 | 3 Processor core software frequency division set Register 23          |

| Table | 4-14 | 4 Chip routing setup register 23                                      |

| Table | 4-15 | Other Function Settings register 24                                   |

| Table | 4-16 | Temperature observation register 25                                   |

| Table | 4-17 | 7 Processor core SRAM adjustment register 25                          |

| Table | 4-18 | B FUSE observation register 25                                        |

| Table | 4-19 | FUSE observation register 26                                          |

| Table | 5-1  | Register 28 for frequency division setting of processor core software |

| Table 5-2 Register 28 for other Function Settings                                                      |

|--------------------------------------------------------------------------------------------------------|

| Table 5-3 Other Function Settings register 29                                                          |

| Table 5-4 Processor core private divider register 29                                                   |

| Table 5-5 Function Settings register 30                                                                |

| Table 5-6 Register 30 for other Functions                                                              |

| Table 5-7 High temperature and frequency drop control register description 30                          |

| Table 5-8 Function Settings register 31                                                                |

| Table 5-9 Other Function Settings Register 32                                                          |

| Table 5-10 Other Function Settings Register 32                                                         |

| Table 5-11 GPIO output enable register 32                                                              |

| Table 6-1 Address access method 33                                                                     |

| Table 6-2 Configuration register instruction access mode                                               |

| Table 6-3 The meanings of registers 34                                                                 |

| Table 6-4 Other Function Settings Register 34                                                          |

| Table 6-5 Node Counter register 36                                                                     |

| Table 7-1 Output enable register 37                                                                    |

| Table 7-2 I/O register 37                                                                              |

| Table 7-3 Interrupt control register 37                                                                |

| Table 7-4 GPIO function reuse Table 38                                                                 |

| Table 7-5 Interrupt control register 39                                                                |

| Table 8-1 Configuration information of instruction set functions implemented by 3A4000 is listed as 43 |

| Table 8-2 List of internal configuration status registers                                              |

| Table 9-1 Shared Cache lock window register configuration 48                                           |

| Table 10-1. Registers and their functions related to interrupt between processor cores                 |

| Table 10- 20 Intercore interrupt and communication registers for processor core No. 0                  |

| Table 10-3 Intercore interrupt and communication registers for Processor core No. 1                    |

| Table 10-4 Intercore interrupt and communication registers for No. 2 processor core                    |

|       | 10-5 Intercore interrupt and communication registers for Processor core No. 3 |

|-------|-------------------------------------------------------------------------------|

|       | 10-6 List of interrupt and communication registers between current processor  |

|       |                                                                               |

| Table | 10-7 Processor inter-core communication register 52                           |

| Table | 11-1 Interrupt control register 55                                            |

| Table | 11-2 IO control register address 56                                       |

|-------|---------------------------------------------------------------------------|

| Table | 11-3 Description of interrupt routing register                            |

| Table | 11-4 Interrupt routing register address 56                                |

| Table | 11-5 Processor core private interrupt status register 57                  |

| Table | 11-6 Register 57 for other Function Settings                              |

| Table | 11-7 Extended IO interrupt enable register 58                             |

| Table | 11-8 Extension IO interrupt Automatic rotation enable register 58         |

| Table | 11-9 Extended IO interrupt status register 58                             |

| Table | 11-10 Extended IO interrupt status register for each processor core 58    |

| Table | 11-11 Description of interrupt pin routing register                       |

| Table | 11-12 Interrupt routing register address 59                               |

| Table | 11-13 Description of interrupt target processor core routing register 60  |

| Table | 11-14 Interrupt target processor core routing register address 60         |

| Table | 11-15 Interrupt target node mapping mode configuration 60                 |

| Table | 11-16 Extended IO interrupt status register for current processor core 61 |

| Table | 11-17 Extended IO interrupt trigger register 61                           |

| Table | 12-1 Temperature sampling register description 63                         |

| Table | 12-2 Extended IO interrupt trigger register 63                            |

| Table | 12-3 High and low temperature interrupt register description 64           |

| Table | 124 High temperature and frequency drop control register description $65$ |

| Table | 12-5 Temperature status detection and control register description 66     |

| Table | 126 Temperature sensor configuration register description $67$ .          |

| Table | 12-7 Temperature sensor data register instruction 67                      |

| Table | 12-8 Monitoring points of temperature sensor                              |

| Table | 13-1 DDR3/4 Address control signal multiplexing 69                        |

| Table | 13-2 Memory controller software visible parameters list 71 $\dots$        |

| Table | 13-3 Memory controller error state observation register 89                |

| Table | 13-4 Memory controller No. 1 error state observation register 90          |

| Table | 14-1 HyperTransport Bus related pin signals 94                            |

| Table | 14-2 Commands that the HyperTransport receiver can receive                |

| Table | 14-3 Command to be sent out in both modes 96                              |

| VII   |                                                                           |

龙芯中科技术有限公司

XII

| Table 14-4 Other Function Settings register 98                                                         |

|--------------------------------------------------------------------------------------------------------|

| Table 14-5 Distribution of address Windows for the four default HyperTransport interfaces              |

| Table 14-6 Distribution of address Windows within the HyperTransport interface of Loongson 3 processor |

| Table 14-7 Address window 99 provided in longson 3A4000 processor HyperTransport interface             |

| Table 14-8 Bus Reset Control register definition 104                                                   |

| Table 14-9 Command, Capabilities Pointer, Capability ID register definition 104                        |

| Table 14-10 Link Config, Link Control register definition 105                                          |

| Table 14-11 Revision ID, Link Freq, Link Error, Link Freq Cap register definition 106                  |

| Table 14-12 Definition of Feature Capability Register                                                  |

| Table 14-13 Error Retry control register 107                                                           |

| Table 14-14 Retry Count register 108                                                                   |

| Table 14-15 Revision ID register 108                                                                   |

| Table 14-16 Interrupt register defines 108                                                             |

| Table 14-17 Dataport register definitions 109                                                          |

| Table 14-18 IntrInfo register definition (1) 109                                                       |

| Table 14-19 IntrInfo register definition (2) 109                                                       |

| Table 14-20 HT bus interrupt vector register definition (1) 111                                        |

| Table 14-21 HT bus interrupt vector register definition (2) 111                                        |

| Table 14-22 HT bus interrupt vector register definition (3) 111                                        |

| Table 14-23 HT bus interrupt vector register definition (4) 111                                        |

| Table 14-24 HT bus interrupt vector register definition (6) 112                                        |

| Table 14-25 HT bus interrupt vector register definition (7) 112                                        |

| Table 14-26 HT bus interrupt vector register definition (8) 112                                        |

| Table 14-27 HT bus interrupt enable register definition (1) 113                                        |

| Table 14-28 HT bus interrupt enable register definition (2) 114                                        |

| Table 14-29 HT bus interrupt enable register definition (3) 114                                        |

| Table 14-30 HT bus interrupt enable register definition (4) 114                                        |

| Table 14-31 HT bus interrupt enabled register definition (5) 114                                       |

|                                                                                                        |

XIII

龙芯中科技术有限公司

Loongson Technology Corporation Limited

Table 14-32 HT bus interrupt enable register definition (6) 114 .....

Table 14-33 HT bus interrupt enabled register definition (7) 115 ....

Table 14-34 HT bus interrupt enable register definition (8) 115 .....

| Table 14-35 Link Train register 115                                                                    |

|--------------------------------------------------------------------------------------------------------|

| Table 14-36 HT bus receive address window 0 enable (external access) register definition 116           |

| Table 14-37 HT bus receive address window 0 Base address (external access) register definition 117     |

| Table 14-38 HT bus receiver address window 1 enables (externally accessible) register definition 117   |

| Table 14-39 HT bus receiver address window 1 Base address (external access) register<br>definition 117 |

| Table 14-40 HT bus receive address window 2 enable (external access) register definition 118           |

| Table 14-41 HT bus receiver address window 2 Base address (external access) register<br>definition 118 |

| Table 14-42 HT bus receive address window 3 enable (external access) register definition 118           |

| Table 14-43 HT bus receiver address window 3 Base address (external access) register definition 119    |

| Table 14-44 HT bus receiver address window 4 enables (externally accessible) register definition 119   |

| Table 14-45 HT bus receiver address window 4 Base address (external access) register<br>definition 119 |

| Table 14-46 Configuration space extension address translation register definition      120             |

| Table 14-47 Extended address translation register definition 120                                       |

| Table 14-48 HT bus POST address window 0 enabled (internal access) 121                                 |

| Table 14-49 HT bus POST address window 0 base address (internal access) 121                            |

| Table 14-50 HT bus POST address window 1 enabling (internal access) 121                                |

| Table 14-51 HT bus POST address window 1 Base address (internal access) 122                            |

| Table 14-52 HT bus can prefetch address window 0 enabling (internal access) 122                        |

| Table 14-53 HT bus prefetchable address window 0 base address (internal access) 122                    |

| Table 14-54 THE HT bus can prefetch address window 1 enabling (internal access) 123                    |

| Table 14-55 HT bus can prefetch address window 1 base address (internal access) 123                    |

XV

龙芯中科技术有限公司 Loongson Technology Corporation Limited

| Table 1 | 14-56 H     | T bus | Uncache       | Address         | window        | 0   | enables (internal access) 123             |

|---------|-------------|-------|---------------|-----------------|---------------|-----|-------------------------------------------|

| Table 1 | 14-57 H     | T Bus | Uncache       | Address         | window        | 0   | base address (internal access) 124        |

| Table 1 | 14-58 H     | T bus | Uncache       | Address         | window        | 1   | enabling (internal access) 124            |

| Table 1 | 14-59 H     | T bus | Uncache       | Address         | window        | 1   | Base address (internal access) 125        |

| Table 1 | 14-60 H     | T bus | Uncache       | Address         | window        | 2   | enables (internal access) 125             |

| Table 1 | 14-61 H     | T Bus | Uncache       | Address         | window        | 2   | Base address (internal access) 125        |

| Table 1 | 14-62 H     | T bus | Uncache       | Address         | window        | 3   | enables (internal access) 125             |

| Table 1 | 14-63 H     | T Bus | Uncache       | Address         | window        | 3   | Base address (internal access) 126        |

|         |             |       |               |                 |               |     | ble (external access) register definition |

| 126     | • • • • • • |       | • • • • • • • | • • • • • • • • | • • • • • • • | • • |                                           |

|         |             |       |               |                 |               |     | e address (external access) register      |

| definit | t10n 12     | 7     |               |                 |               |     |                                           |

| Table 14-66 HT bus P2P address window 1 enables (externally accessible) register definition 127 |

|-------------------------------------------------------------------------------------------------|

| Table 14-67 HT bus P2P address window 1 base address (external access) register definition 127  |

| Table 14-68 Controller parameter configuration register 0 defines 127                           |

| Table 14-69 Controller parameter configuration register 1 defines 128                           |

| Table 14-70 receives diagnostic register 130                                                    |

| Table 14-71 PHY status register 130                                                             |

| Table 14-72 sends the cache size register 131                                                   |

| Table 14-73 Data send cache size register 131                                                   |

| Table 14-74 Send cache debug register 132                                                       |

| Table 14-75 Receive buffer initial register 133                                                 |

| Table 14-76 Short timeout register of Training 0                                                |

| Table 14-77 Training O timeout long count register 134                                          |

| Table 14-78 Register 134 of Training 1                                                          |

| Table 14-79 Training 2 counting register 135                                                    |

| Table 14-80 Training 3 counting register 135                                                    |

| Table 14-81 Software frequency configuration register 136                                       |

| Table 14-82 Impedance matching control register 137                                             |

| Table 14-83 PHY configuration register 137                                                      |

| Table 14-84 Link Initialization debug register 139                                              |

| Table 14-85 LDT debug register 1139                                                             |

| Table 14-86 LDT debug register 2139                                                             |

| Table 14-87 LDT debug register 3139                                                             |

| Table 14-88 LDT debug register 4140                                                             |

| Table 14-89 LDT debug register 5140                                                             |

| Table 14-90 LDT debug register 5140                                                             |

| Table 14-91 HT TX POST ID WIN0141                                                               |

| Table 14-92 HT TX POST ID WIN1141                                                               |

| Table 14-93 HT TX POST ID WIN2141                                                               |

| Table 14-94 HT TX POST ID WIN3141                                                               |

|                                                                                                 |

| Table | 14-95 | НТ | RX | INT | TRANS | L0142 |  |

|-------|-------|----|----|-----|-------|-------|--|

| Table | 14-96 | НТ | RX | INT | TRANS | Hi142 |  |

| Table | 15-1 | SPI controller address space distribution 157   |

|-------|------|-------------------------------------------------|

| Table | 16-1 | Chip feature register 168                       |

| Table | 16-2 | Manufacturer name register 169                  |

| Table | 16-3 | Chip name register 169                          |

| Table | 16-4 | HT RX INT TRANS LO171                           |

| Table | 16-5 | HT RX INT TRANS Hi171                           |

| Table | 16-6 | Other Function Settings register 172            |

| Table | 16-7 | Processor inter-core communication register 172 |

#### 1 An overview of the

#### 1.1 Introduction to loong chip series processor

The godson processor mainly consists of three series. Loongson No. 1 processor and its IP series are mainly for embedded applications, Loongson No. 2 superstandard processor and its IP series are mainly for desktop applications, and Loongson No. 3 multi-core processor series are mainly for server and high-performance computer applications. According to the needs of the application, part of the loongson 2 can also be oriented towards part of the high-end embedded

Yes, some low-end Longson 3 can also be used for some desktop applications. The three series developed in parallel.

Based on the scalable multi-core interconnection architecture, the Loongson 3 multi-core series processor integrates multiple high-performance processor cores and a large number of 2-level Caches on a single chip, and realizes multi-chip interconnection through high-speed I/O interface to form a larger scale system.

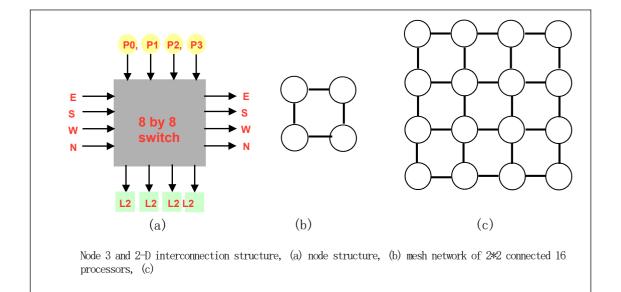

The telescopic interconnection structure adopted by Loongson no. 3 is shown in Figure 1-1 below. The godson 3 and more pieces system interconnection ports with similar to node to implement interconnection structure unit, in which each node is composed of 8 \* 8 cross switch, each cross switch connected four cores and four Shared Cache, and the east (E) south west (W) north (N) (N) interconnection of other nodes in four directions.

Figure 1-1 System structure of No. 3 Loong Chip

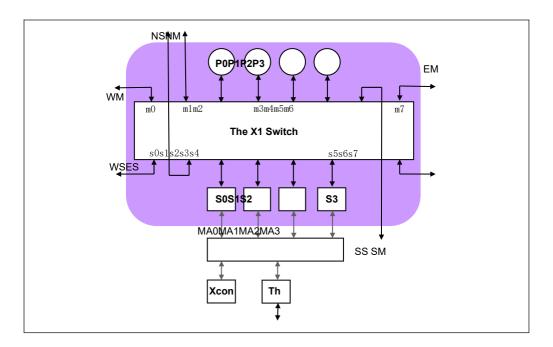

The node structure of No.3 is shown in Figure 1-2 below. Each node has two levels of AXI switch to connect processor and share

Cache, memory controller, and IO controller. The first level of AXI cross-switches (called the X1 Switch, or X1 for short) connects the processor to the Shared Cache. The second level cross Switch (called the X2 Switch, or X2 for short) connects the Shared Cache to the memory controller.

Figure 1-2 Structure of No. 3 node of the Loong Chip

In each node, the X1 cross switch of up to 8\*8 connects four GS464 processor cores through four Master ports

(P0, P1, P2, P3), connect four interleave Shared Cache blocks uniformly addressed through four Slave ports (S0, S1, S2, S3), and connect four Master/Slave ports to other nodes or IO nodes in the east, south, west, and north directions (EM/ES, SM/SS, WM/WS, NM/NS).

X2 cross-switch connects four Shared caches through four Master ports, at least one Slave port connects to a memory controller, at least one Slave port connects to a cross-switch configuration module (Xconf), which is used to configure the address window of X1 and X2 of this node. You can also connect more memory controllers and IO ports as needed.

#### 1.2 Introduction to Loongson 3A4000

Longshon 3A4000 is a quad-core longshon processor manufactured by a 28nm process with a stable operating frequency of 1.5-2.0GHz. Its main technical features are as follows:

- Four 64-bit quad-emission superstandard GS464V high-performance processor cores are integrated on the chip.

- Integrated 8MB split Shared three-level Cache (composed of 4 individual modules, each with a capacity of 2MB);

- Maintain Cache consistency of multi-core and I/O DMA access through directory protocol;

- Integrated two 64-bit DDR3/4 controllers with ECC and 800MHz on the chip;

- Two 16-bit HyperTransport controllers (HT) are integrated on the chip;

- Each 16-bit HT port is divided into two 8-way HT ports for use.

- Two I2C, one UART, one SPI and 16-channel GPIO interfaces are integrated on the chip.

On the basis of 3A2000/3A3000, the top structure design of Loongson 3A4000 is greatly optimized, and the main improvements are as follows:

- The structure of on-chip interconnection is adjusted and address routing is simplified. RING structure is adopted for the interconnection between IO modules.

- The bandwidth utilization and cross-chip delay of HT controller are optimized.

- Optimized the structure of memory controller, increased the support of MEMORY controller DDR4, and supported memory slot connection acceleration card;

- The register space and access mode are standardized, and the REGISTER access mechanism of CSR is introduced.

- The interrupt controller structure is optimized and the support vector interrupt hardware distribution mechanism is optimized.

- Added 8 way interconnection support.

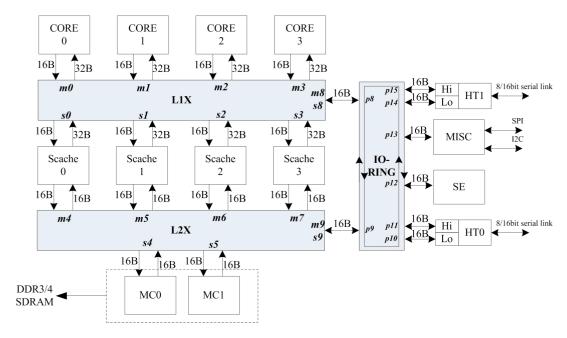

The overall architecture of Loongson 3A4000 chip is realized based on multi-level interconnection. The structure is shown in Figure 1-3 below.

Figure 1-3 Structure of Loongson 3A4000 chip

The first interconnection USES a 5x5 cross switch for connecting four GS464v cores (as the primary device), four Shared Cache modules (as the slave device), and an IO port to the IO-Ring. IO port USES one Master and one Slave.

The second interconnection USES a 5x3 cross-switch to connect four Shared Cache modules (as the primary device), two DDR3/4 memory controllers, and an IO port to the IO-Ring.

Io-ring contains 8 ports, connection includes 4 HT controller, MISC module, SE module and two-stage cross switch. Two HT controllers (LO/HI) share the 16-bit HT bus, which can be used as two 8-bit HT buses, or lo can monopolized the 16-bit HT bus. HT controller integrates a DMA controller, which is responsible for DMA control of IO and maintenance of inter-chip consistency.

The interconnection structure USES a read-write separated data channel with a width of 128 bits and operates at the same frequency as the processor core to provide high-speed on-chip data transmission. In addition, a one-stage cross-switch connects the four processor cores to the scache's read data channel for 256 bits to improve the read bandwidth of the on-chip processor cores accessing scache.

#### 2 System configuration and control

#### 2.1 Chip operation mode

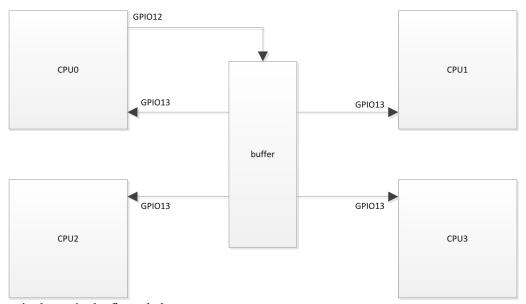

According to the structure of the system, longson 3A4000 mainly includes two working modes:

- Single chip mode. The system contains only one piece of longson 3A4000, which is a symmetric multiprocessor system (SMP).

- Multi-chip interconnection mode. The system consists of 2, 4 or 8 loongson 3A4000 connected through HT port to form a non-uniform access multiprocessor system (CC-NUMA).

#### 2.2 Control pin description

Main control pins include DO\_TEST, ICCC\_EN, NODE\_ID[2:0], CLKSEL[9:0], CHIP\_CONFIG[5:0].

Table 2-1 Description of control pins

|               | rubic 2 i bescription of control pins |                                                                                                       |                                                                    |  |  |  |

|---------------|---------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

| signal        | Pull up<br>and<br>down                |                                                                                                       | role                                                               |  |  |  |

| Do TEGE       | 0.4                                   | 1 'b1 represents the                                                                                  | e functional mode                                                  |  |  |  |

| DO_TEST       | On the pull                           | 1 'b0 represents the                                                                                  | e test mode                                                        |  |  |  |

| ICCC_EN       | The<br>drop-<br>down                  | 1 'B1 represents the multi-chip consistent interconnection mode 1 'b0 represents the single-chip mode |                                                                    |  |  |  |

| NODE_ID [2-0] |                                       | Represents the pro<br>mode                                                                            | cessor number in multi-chip consistent interconnection             |  |  |  |

|               |                                       | HT clock<br>control                                                                                   |                                                                    |  |  |  |

|               |                                       | signal                                                                                                | role                                                               |  |  |  |

|               |                                       | CLKSEL [9]                                                                                            | 1 'B1: means that HT PLL clock is controlled by CLKSEL[9:4]        |  |  |  |

|               |                                       |                                                                                                       | 1 'b0: The initial frequency multiplier is 1, which can            |  |  |  |

| CLKSEL [9:0]  |                                       |                                                                                                       | be reconfigured by the software                                    |  |  |  |

| [۶۰۰]         |                                       | CLKSEL [8]                                                                                            | 1 'b1: Means HT PLL USES SYSCLK clock input                        |  |  |  |

|               |                                       |                                                                                                       | 1 'b0: means HT PLL adopts differential clock input                |  |  |  |

|               |                                       |                                                                                                       | 2 'b00 means the PHY clock frequency is 1.6ghz                     |  |  |  |

|               |                                       | CLKSEL [but]                                                                                          | 2 'b01 means the PHY clock frequency is 3.2ghz (reference clock is |  |  |  |

|               |                                       | . ,                                                                                                   | 1.6ghz at 25MHz)                                                   |  |  |  |

|               |                                       |                                                                                                       | 2 'b10 means THE PHY clock frequency is 1.2ghz                     |  |  |  |

|               |                                       |                                                                                                       | 2 'b11 means THE PHY clock frequency is 2.4ghz                     |  |  |  |

|               |                                       | CLKSEL [5]                                                                                            | 1 'b1: Refers to HT PLL clock is in bypass mode, direct            |  |  |  |

|               |                                       |                                                                                                       | External input 100MHz/25MHz reference clock is used                |  |  |  |

|             | CLKSEL [4]                               | The 1-reference clock is 25MHz and the 0-                |  |  |  |

|-------------|------------------------------------------|----------------------------------------------------------|--|--|--|

|             |                                          |                                                          |  |  |  |

|             |                                          |                                                          |  |  |  |

|             | CLKSEL (3:2)                             | The output frequency                                     |  |  |  |

|             | 2 'b00                                   | 466 MHZ                                                  |  |  |  |

|             |                                          | 100                                                      |  |  |  |

|             | 2 'b01                                   | 600 MHZ                                                  |  |  |  |

|             | 2 'b10                                   | Software configuration (PLL clock multiplier 1.6-3.2ghz) |  |  |  |

|             | 2 'bl1                                   | SYSCLK (100 MHZ / 25 MHZ)                                |  |  |  |

|             |                                          |                                                          |  |  |  |

|             |                                          |                                                          |  |  |  |

|             | Main clock control (maximum frequency of |                                                          |  |  |  |

|             | CLKSEL [1:0]                             | The output frequency                                     |  |  |  |

|             | 2 'b00                                   | 1 GHZ.                                                   |  |  |  |

|             | 2 'b01                                   | 2 GHZ.                                                   |  |  |  |

|             | 2 'b10                                   | Software configuration (PLL clock                        |  |  |  |

|             | 2 'bl1                                   | SYSCLK (100 MHZ / 25 MHZ)                                |  |  |  |

|             | Chip                                     |                                                          |  |  |  |

|             | CHIP_CONFIG [0]                          | SE functional enablement                                 |  |  |  |

|             | CHIP_CONFIG [1]                          | Default HT Gen1 mode                                     |  |  |  |

|             | CHIP_CONFIG [2]                          | reserve                                                  |  |  |  |

| CHIP_CONFIG | CHIP_CONFIG [3]                          | HtO/1-hi enters consistency mode by default              |  |  |  |

| [beat]      |                                          | and is used to support 8-way mutual                      |  |  |  |

|             | CHIP_CONFIG [4]                          | HT logic function interchange, HTO/HT1                   |  |  |  |

|             | CHIP CONFIG [5]                          |                                                          |  |  |  |

|             | 51111 _00111 10 [0]                      | on only clock desagoing chaster (Bebb)                   |  |  |  |

#### 3 Physical address space distribution

The system physical address distribution of The Loongson 3 series processor adopts the globally accessible hierarchical addressing design to ensure that

System development extension compatibility. The physical address width of the entire system is 48 bits. According to the address of the high 4 bits, the entire address is empty

In other words, each node is allocated a 44-bit address space.

#### 3.1 Physical address space distribution between nodes

Longson 3A4000 processor can directly use 2/4/8 3A4000 chips to build CC-NUMA system. The processor number of each chip is determined by pin NODEID. The address space distribution of each chip is as follows:

Table 3-1 Global address distribution of the system at node level

| Chip NODEID | Address [47:44] | The starting address | End address       |

|-------------|-----------------|----------------------|-------------------|

| 0           | 0               | 0 x0000_0000_0000    | 0 x0fff_ffff_ffff |

| 1           | 1               | 0 x1000_0000_0000    | 0 x1fff_ffff_ffff |

| 2           | 2               | 0 x2000_0000_0000    | 0 x2fff_ffff_ffff |

| 3           | 3               | 0 x3000_0000_0000    | 0 x3fff_ffff_ffff |

| 4           | 4               | 0 x4000_0000_0000    | 0 x4fff_ffff_ffff |

| 5           | 5               | 0 x5000_0000_0000    | 0 x5fff_ffff_ffff |

| 6           | 6               | 0 x6000_0000_0000    | 0 x6fff_ffff_ffff |

| 7           | 7               | 0 x7000_0000_0000    | 0 x7fff_ffff_ffff |

When the number of system nodes is less than 8, the nodemask field of the route setting register (0x1FE00400) should be set to ensure that the response can be obtained even without the address of the physical node when guess access occurs. (2 channels: 0x1; Route 4:0x3)

#### 3.2 Physical address space distribution within nodes

The single node 4-core configuration is adopted for the longson 3A4000, so the DDR memory controller integrated with the longson 3A4000 chip and the corresponding address of the HT bus are all contained in the 44-bit address space from 0x0 (including) to 0x1000\_0000\_0000 (excluding). Within each node, the 44-bit address space is further divided among all devices connected within the node, and requests are routed to four Shared Cache modules only if the access type is cached. Depending on the configuration of the chip and system structure, if there is no slave device connected on a port, the corresponding address space is reserved address space and is not allowed to access.

The address space corresponding to each slave terminal of internal interconnection of Loongson 3A4000 chip is as follows:

Table 3-2 Address distribution in nodes

| equip<br>ment     | Address [43:40] | The starting address of a node | Node end address |

|-------------------|-----------------|--------------------------------|------------------|

| MC0               | 4               | 0 x400_0000_0000               | 0 x4ff_ffff_ffff |

| MC1               | 5               | 0 x500_0000_0000               | 0 x5ff_ffff_ffff |

| SE                | С               | 0 xc00_0000_0000               | 0 xcff_ffff_ffff |

| HT0 Lo controller | a.              | 0 xa00_0000_0000               | 0 xaff_ffff_ffff |

| HT0 Hi controller | b               | 0 xb00_0000_0000               | 0 xbff_ffff_ffff |

| HT1 Lo controller | e               | 0 xe00_0000_0000               | 0 xeff_ffff_ffff |

| HT1 Hi controller | f               | 0 xf00_0000_0000               | 0 xfff_ffff_ffff |

Different from the mapping relationship of directional ports, longson 3A4000 can determine the cross-addressing mode of Shared Cache based on the actual application access behavior. The address space corresponding to the four Shared Cache modules in the node is determined according to some two-bit selection bits of address bits, and can be dynamically configured by software. A configuration register called SCID\_SEL is set up to determine the address selection bit, as shown in the table below. By default, the distribution takes the form of [7:6] address hash, in which the [7:6] two digits of the address determine the corresponding Shared Cache number. The register address is 0x3FF00400 or 0x1fe00400.

Table 3-3 SCID SEL address bit Settings

| SCID_SEL | Address bit selection | SCID_SEL | Address bit selection |

|----------|-----------------------|----------|-----------------------|

| 4 'h0    | 7:6                   | 4 'h8    | "                     |

| 4 'h1    | 9:8                   | 4 'h9    | Thus for              |

| 4 'h2    | "                     | 4 'ha    | But after             |

| 4 'h3    | She<br>answered       | 4 'hb    | then                  |

| 4 'h4    | The lowest            | 4 'hc    | charm                 |

| 4 'h5    | "                     | 4 'hd    | 33:32                 |

| 4 'h6    | 7                     | 4 'he    | "                     |

| 4 'h7    | mark                  | 4 'hf    | meanwhile             |

The default distribution of the internal 44-bit physical address of each node in Longson 3A4000 processor is shown in the following table:

Table 4-4 Physical address distribution in nodes 3-4

| Address<br>range                                                     | To access attributes | destination |

|----------------------------------------------------------------------|----------------------|-------------|

| Addr [43:40] = = 4 "ha                                               | Local node,uncache   | HT0_LO      |

| Addr [43:40] = = '4 hb                                               | Local node,uncache   | HT0_HI      |

| Addr [43:40] = = 4 'hc                                               | Local node,uncache   | SE          |

| 'he addr [43:40] = = 4                                               | Local node,uncache   | HT1_LO      |

| Addr [43:40] = = '4 hf                                               | Local node,uncache   | HT1_HI      |

| 0x10000000-0x1FFFFFFf, 0x3FF00000-0x3FF0FFff (closed)                | Local node,uncache   | MISC        |

| Mc Interleave is 0 and is not the above address                      | Local node,uncache   | MC0         |

| Mc Interleave is 1 and is not the above address                      | Local node,uncache   | MC1         |

| Scache interleave is 0(address bit selection determined by scID sel) | Local node,cache     | Scache0     |

| Scache interleave is 1(address bit selection determined by SCID sel) | Local node,cache     | Scache1     |

| Scache interleave is 2(address bit selection determined by SCID sel) | Local node,cache     | Scache2     |

| Scache interleave is 3(address bit selection determined by SCID_sel) | Local node,cache     | Scache3     |

#### 3.3 Address routing distribution and configuration

The routing of Loongson 3A4000 is mainly realized through the two-stage cross switch and IO-ring of the system. The software can carry out routing configuration for the requests received by each Master port. Each Master port has 8 address Windows, which can complete the target routing selection of 8 address Windows. Each address window is composed of three 64-bit registers, BASE, MASK and MMAP. The BASE is aligned with K bytes. MASK adopts a format similar to network MASK in which the high digit is 1. The low four-digit MMAP represents the number corresponding to the target Slave port, MMAP[4] represents the enabled point, MMAP[5] represents the enabled block, MMAP[6] represents the enabled window.

Table 3-5 MMAP field corresponding to the space access properties

| [7]        | [6]                           | [5]        | [4]        |

|------------|-------------------------------|------------|------------|

| The window | Allows interleaving access to | Allow the  | Allowed to |

| can make   | SCACHE/ memory                | block read | take to    |

Window hit formula :(IN ADDR & MASK) == BASE

As the default route is fixed, the configuration window is closed when starting power on, and the system software is required to enable configuration of the loongson no. 3.

SCACHE/ memory interleave access configuration enabled, Slave number is only valid when 0 or 4. Zero represents routing to SCACHE and it is up to SCID\_SEL to decide how to interleave access across the four SCACHE. A 4 represents routing to memory, with interleave\_bit deciding how to interleave access between the two MCS.

The address window conversion register is shown in the following table.

Table 3-6 Address window register table

|              | Table 5-6 Address V | vindow legiste. | r table         |

|--------------|---------------------|-----------------|-----------------|

| address      | register            | address         | register        |

| 0 x3ff0_2000 | CORE0_WIN0_BASE     | 0 x3ff0_2100    | CORE1_WIN0_BASE |

| 0 x3ff0_2008 | CORE0_WIN1_BASE     | 0 x3ff0_2108    | CORE1_WIN1_BASE |

| 0 x3ff0_2010 | CORE0_WIN2_BASE     | 0 x3ff0_2110    | CORE1_WIN2_BASE |

| 0 x3ff0_2018 | CORE0_WIN3_BASE     | 0 x3ff0_2118    | CORE1_WIN3_BASE |

| 0 x3ff0_2020 | CORE0_WIN4_BASE     | 0 x3ff0_2120    | CORE1_WIN4_BASE |

| 0 x3ff0_2028 | CORE0_WIN5_BASE     | 0 x3ff0_2128    | CORE1_WIN5_BASE |

| 0 x3ff0_2030 | CORE0_WIN6_BASE     | 0 x3ff0_2130    | CORE1_WIN6_BASE |

| 0 x3ff0_2038 | CORE0_WIN7_BASE     | 0 x3ff0_2138    | CORE1_WIN7_BASE |

| 0 x3ff0_2040 | CORE0_WIN0_MASK     | 0 x3ff0_2140    | CORE1_WIN0_MASK |

| 0 x3ff0_2048 | CORE0_WIN1_MASK     | 0 x3ff0_2148    | CORE1_WIN1_MASK |

| 0 x3ff0_2050 | CORE0_WIN2_MASK     | 0 x3ff0_2150    | CORE1_WIN2_MASK |

| 0 x3ff0_2058 | CORE0_WIN3_MASK     | 0 x3ff0_2158    | CORE1_WIN3_MASK |

| 0 x3ff0_2060 | CORE0_WIN4_MASK     | 0 x3ff0_2160    | CORE1_WIN4_MASK |

| 0 x3ff0_2068 | CORE0_WIN5_MASK     | 0 x3ff0_2168    | CORE1_WIN5_MASK |

| 0 x3ff0_2070 | CORE0_WIN6_MASK     | 0 x3ff0_2170    | CORE1_WIN6_MASK |

| 0 x3ff0_2078 | CORE0_WIN7_MASK     | 0 x3ff0_2178    | CORE1_WIN7_MASK |

| 0 x3ff0_2080 | CORE0_WIN0_MMAP     | 0 x3ff0_2180    | CORE1_WIN0_MMAP |

| 0 x3ff0_2088 | CORE0_WIN1_MMAP     | 0 x3ff0_2188    | CORE1_WIN1_MMAP |

| 0 x3ff0_2090 | CORE0_WIN2_MMAP     | 0 x3ff0_2190    | CORE1_WIN2_MMAP |

| 0 x3ff0_2098 | CORE0_WIN3_MMAP     | 0 x3ff0_2198    | CORE1_WIN3_MMAP |

| 0 x3ff0_20a0 | CORE0_WIN4_MMAP     | 0 x3ff0_21a0    | CORE1_WIN4_MMAP |

| 0 x3ff0_20a8 | CORE0_WIN5_MMAP     | 0 x3ff0_21a8    | CORE1_WIN5_MMAP |

| 0 x3ff0_20b0 | CORE0_WIN6_MMAP     | 0 x3ff0_21b0    | CORE1_WIN6_MMAP |

龙芯中科技术有限公司

| 0 x3ff0 20b8         COREO_WIN7_MMAP         0 x3ff0 21b8         COREI_WIN7_MMAP           0 x3ff0 2200         CORE2_WIN0_BASE         0 x3ff0 2300         CORE3_WIN0_BASE           0 x3ff0 2200         CORE2_WIN1_BASE         0 x3ff0 2300         CORE3_WIN1_BASE           0 x3ff0 2210         CORE2_WIN2_BASE         0 x3ff0 2310         CORE3_WIN2_BASE           0 x3ff0 2210         CORE2_WIN3_BASE         0 x3ff0 2318         CORE3_WIN4_BASE           0 x3ff0 2220         CORE2_WIN4_BASE         0 x3ff0 2320         CORE3_WIN4_BASE           0 x3ff0 2228         CORE2_WIN5_BASE         0 x3ff0 2330         CORE3_WIN4_BASE           0 x3ff0 2230         CORE2_WIN5_BASE         0 x3ff0 2338         CORE3_WIN6_BASE           0 x3ff0 2238         CORE2_WIN6_BASE         0 x3ff0 2338         CORE3_WIN6_BASE           0 x3ff0 2240         CORE2_WIN0_MASK         0 x3ff0 2348         CORE3_WIN0_MASK           0 x3ff0 2244         CORE2_WIN0_MASK         0 x3ff0 2350         CORE3_WIN0_MASK           0 x3ff0 2250         CORE2_WIN2_MASK         0 x3ff0 2350         CORE3_WIN0_MASK           0 x3ff0 2256         CORE2_WIN3_MASK         0 x3ff0 2356         CORE3_WIN3_MASK           0 x3ff0 2266         CORE2_WIN4_MASK         0 x3ff0 2366         CORE3_WIN4_MASK                                                                                                                                   |              | Mil               | 5A4000 足種1   | 時可行地区内了加          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|--------------|-------------------|

| 0 x3ff0 2208         CORE2_WIN_BASE         0 x3ff0 2310         CORE3_WIN_BASE         0 x3ff0 2310         CORE3_WIN_BASE           0 x3ff0 2218         CORE2_WIN_BASE         0 x3ff0 2318         CORE3_WIN_BASE         CORE3_WIN_BASE           0 x3ff0 2220         CORE2_WIN_BASE         0 x3ff0 2320         CORE3_WIN_BASE         CORE3_WIN_BASE           0 x3ff0 2230         CORE2_WIN_BASE         0 x3ff0 2338         CORE3_WIN_BASE         O x3ff0 2338           0 x3ff0 2230         CORE2_WIN_BASE         0 x3ff0 2338         CORE3_WIN_BASE         O x3ff0 2338           0 x3ff0 2238         CORE2_WIN_BASE         0 x3ff0 2338         CORE3_WIN_BASE         O x3ff0 2338           0 x3ff0 2240         CORE2_WIN_BASE         0 x3ff0 2340         CORE3_WIN_BASE         O x3ff0 2340           0 x3ff0 2248         CORE2_WIN_MASK         0 x3ff0 2350         CORE3_WIN_MASK         O x3ff0 2350           0 x3ff0 2250         CORE2_WIN_MASK         0 x3ff0 2358         CORE3_WIN_MASK         O x3ff0 2358           0 x3ff0 2268         CORE2_WIN_MASK         0 x3ff0 2360         CORE3_WIN_MASK         O x3ff0 2360           0 x3ff0 2270         CORE2_WIN_MASK         0 x3ff0 2370         CORE3_WIN_MASK           0 x3ff0 2278         CORE2_WIN_MASK         0 x3ff0 2378         CORE3_WIN_MASK                                                                                                      | 0 x3ff0_20b8 | CORE0_WIN7_MMAP   | 0 x3ff0_21b8 | CORE1_WIN7_MMAP   |

| 0 x3ff0 2210         CORE2 WIN BASE         0 x3ff0 2310         CORE3 WIN BASE           0 x3ff0 2218         CORE2 WIN BASE         0 x3ff0 2318         CORE3 WIN BASE           0 x3ff0 2220         CORE2 WIN BASE         0 x3ff0 2320         CORE3 WIN BASE           0 x3ff0 2228         CORE2 WIN BASE         0 x3ff0 2328         CORE3 WIN BASE           0 x3ff0 2238         CORE2 WIN BASE         0 x3ff0 2330         CORE3 WIN BASE           0 x3ff0 2238         CORE2 WIN BASE         0 x3ff0 2338         CORE3 WIN BASE           0 x3ff0 2240         CORE2 WIN MASK         0 x3ff0 2348         CORE3 WIN MASK           0 x3ff0 2248         CORE2 WIN MASK         0 x3ff0 2348         CORE3 WIN MASK           0 x3ff0 2258         CORE2 WIN MASK         0 x3ff0 2358         CORE3 WIN MASK           0 x3ff0 2258         CORE2 WIN MASK         0 x3ff0 2360         CORE3 WIN MASK           0 x3ff0 2260         CORE2 WIN MASK         0 x3ff0 2368         CORE3 WIN MASK           0 x3ff0 2260         CORE2 WIN MASK         0 x3ff0 2368         CORE3 WIN MASK           0 x3ff0 2270         CORE2 WIN MASK         0 x3ff0 2378         CORE3 WIN MASK           0 x3ff0 2270         CORE2 WIN MASK         0 x3ff0 2378         CORE3 WIN MASK           0 x3ff0 2280                                                                                                                                        | 0 x3ff0_2200 | CORE2_WIN0_BASE   | 0 x3ff0_2300 | CORE3_WIN0_BASE   |

| 0 x3ff0 2218         CORE2 WIN BASE         0 x3ff0 2318         CORE3 WIN BASE           0 x3ff0 2220         CORE2 WIN4 BASE         0 x3ff0 2320         CORE3 WIN4 BASE           0 x3ff0 2228         CORE2 WIN5 BASE         0 x3ff0 2338         CORE3 WIN5 BASE           0 x3ff0 2230         CORE2 WIN6 BASE         0 x3ff0 2330         CORE3 WIN5 BASE           0 x3ff0 2238         CORE2 WIN7 BASE         0 x3ff0 2338         CORE3 WIN7 BASE           0 x3ff0 2248         CORE2 WIN0 MASK         0 x3ff0 2340         CORE3 WIN7 MASK           0 x3ff0 2248         CORE2 WIN1 MASK         0 x3ff0 2348         CORE3 WIN1 MASK           0 x3ff0 2250         CORE2 WIN3 MASK         0 x3ff0 2358         CORE3 WIN2 MASK           0 x3ff0 2250         CORE2 WIN4 MASK         0 x3ff0 2358         CORE3 WIN4 MASK           0 x3ff0 2260         CORE2 WIN4 MASK         0 x3ff0 2360         CORE3 WIN4 MASK           0 x3ff0 2268         CORE2 WIN5 MASK         0 x3ff0 2360         CORE3 WIN4 MASK           0 x3ff0 2270         CORE2 WIN5 MASK         0 x3ff0 2378         CORE3 WIN5 MASK           0 x3ff0 2288         CORE2 WIN5 MASK         0 x3ff0 2378         CORE3 WIN7 MASK           0 x3ff0 2286         CORE2 WIN5 MMAP         0 x3ff0 2380         CORE3 WIN7 MMAP                                                                                                                                     | 0 x3ff0_2208 | CORE2_WIN1_BASE   | 0 x3ff0_2308 | CORE3_WIN1_BASE   |

| 0 x3ff0 2220         CORE2_WIN4_BASE         0 x3ff0 2320         CORE3_WIN5_BASE         0 x3ff0 2328         CORE3_WIN5_BASE           0 x3ff0 2230         CORE2_WIN5_BASE         0 x3ff0 2330         CORE3_WIN6_BASE         0 x3ff0 2330         CORE3_WIN6_BASE           0 x3ff0 2238         CORE2_WIN6_BASE         0 x3ff0 2338         CORE3_WIN6_BASE         0 x3ff0 2338         CORE3_WIN6_BASE           0 x3ff0 2240         CORE2_WIN6_MASK         0 x3ff0 2340         CORE3_WIN6_MASK         0 x3ff0 2348         CORE3_WIN6_MASK           0 x3ff0 2258         CORE2_WIN6_MASK         0 x3ff0 2350         CORE3_WIN1_MASK         0 x3ff0 2250         CORE3_WIN2_MASK           0 x3ff0 2258         CORE2_WIN3_MASK         0 x3ff0 2358         CORE3_WIN3_MASK         0 x3ff0 2358         CORE3_WIN3_MASK           0 x3ff0 2260         CORE2_WIN3_MASK         0 x3ff0 2368         CORE3_WIN5_MASK         0 x3ff0 2368         CORE3_WIN5_MASK           0 x3ff0 2268         CORE2_WIN6_MASK         0 x3ff0 2370         CORE3_WIN5_MASK         0 x3ff0 2370         CORE3_WIN5_MASK           0 x3ff0 2270         CORE3_WIN6_MASK         0 x3ff0 2378         CORE3_WIN5_MASK         0 x3ff0 2378         CORE3_WIN5_MASK           0 x3ff0 2280         CORE2_WIN6_MAP         0 x3ff0 2388         CORE3_WIN6_MAP         0 x3ff0 2390         <                                                                 | 0 x3ff0_2210 | CORE2_WIN2_BASE   | 0 x3ff0_2310 | CORE3_WIN2_BASE   |

| 0 x3ff0 2228         CORE2_WIN5_BASE         0 x3ff0 2330         CORE3_WIN6_BASE         0 x3ff0 2330         CORE3_WIN6_BASE           0 x3ff0 2238         CORE2_WIN6_BASE         0 x3ff0 2338         CORE3_WIN6_BASE         0 x3ff0 2338         CORE3_WIN7_BASE           0 x3ff0 2240         CORE2_WIN0_MASK         0 x3ff0 2340         CORE3_WIN0_MASK         0 x3ff0 2348         CORE3_WIN1_MASK           0 x3ff0 2250         CORE2_WIN2_MASK         0 x3ff0 2350         CORE3_WIN2_MASK         0 x3ff0 2350         CORE3_WIN2_MASK           0 x3ff0 2250         CORE2_WIN3_MASK         0 x3ff0 2358         CORE3_WIN3_MASK         0 x3ff0 2358         CORE3_WIN3_MASK           0 x3ff0 2250         CORE2_WIN4_MASK         0 x3ff0 2360         CORE3_WIN4_MASK         0 x3ff0 2360         CORE3_WIN3_MASK           0 x3ff0 2260         CORE2_WIN4_MASK         0 x3ff0 2360         CORE3_WIN5_MASK         0 x3ff0 2360         CORE3_WIN5_MASK           0 x3ff0 2270         CORE2_WIN5_MASK         0 x3ff0 2370         CORE3_WIN6_MASK         0 x3ff0 2370         CORE3_WIN6_MASK           0 x3ff0 2288         CORE2_WIN6_MASK         0 x3ff0 2370         CORE3_WIN6_MASK         0 x3ff0 2378         CORE3_WIN6_MASK           0 x3ff0 2280         CORE2_WIN6_MAP         0 x3ff0 2388         CORE3_WIN6_MAP         0 x3ff0 2388         <                                                                 | 0 x3ff0_2218 | CORE2_WIN3_BASE   | 0 x3ff0_2318 | CORE3_WIN3_BASE   |

| 0 x3ff0 2230         CORE2 WIN6 BASE         0 x3ff0 2330         CORE3 WIN6 BASE           0 x3ff0 2238         CORE2 WIN7 BASE         0 x3ff0 2338         CORE3 WIN7 BASE           0 x3ff0 2240         CORE2 WIN0 MASK         0 x3ff0 2340         CORE3 WIN0 MASK           0 x3ff0 2248         CORE2 WIN1 MASK         0 x3ff0 2348         CORE3 WIN2 MASK           0 x3ff0 2250         CORE2 WIN2 MASK         0 x3ff0 2350         CORE3 WIN2 MASK           0 x3ff0 2258         CORE2 WIN3 MASK         0 x3ff0 2360         CORE3 WIN4 MASK           0 x3ff0 2260         CORE2 WIN5 MASK         0 x3ff0 2368         CORE3 WIN4 MASK           0 x3ff0 2268         CORE2 WIN5 MASK         0 x3ff0 2370         CORE3 WIN5 MASK           0 x3ff0 2270         CORE2 WIN6 MASK         0 x3ff0 2370         CORE3 WIN6 MASK           0 x3ff0 2278         CORE2 WIN7 MASK         0 x3ff0 2370         CORE3 WIN6 MASK           0 x3ff0 2280         CORE2 WIN7 MASK         0 x3ff0 2380         CORE3 WIN0 MAP           0 x3ff0 2280         CORE2 WIN7 MASK         0 x3ff0 2388         CORE3 WINA MAP           0 x3ff0 2298         CORE2 WINA MAP         0 x3ff0 2388         CORE3 WINA MAP           0 x3ff0 2298         CORE2 WIN3 MAP         0 x3ff0 2380         CORE3 WINA MAP <td< td=""><td>0 x3ff0_2220</td><td>CORE2_WIN4_BASE</td><td>0 x3ff0_2320</td><td>CORE3_WIN4_BASE</td></td<>                             | 0 x3ff0_2220 | CORE2_WIN4_BASE   | 0 x3ff0_2320 | CORE3_WIN4_BASE   |

| 0 x3ff0 2238         CORE2 WIN7 BASE         0 x3ff0 2340         CORE3 WIN7 BASE           0 x3ff0 2240         CORE2 WIN0 MASK         0 x3ff0 2340         CORE3 WIN0 MASK           0 x3ff0 2248         CORE2 WIN1 MASK         0 x3ff0 2348         CORE3 WIN1 MASK           0 x3ff0 2250         CORE2 WIN2 MASK         0 x3ff0 2350         CORE3 WIN2 MASK           0 x3ff0 2258         CORE2 WIN3 MASK         0 x3ff0 2358         CORE3 WIN3 MASK           0 x3ff0 2260         CORE2 WIN4 MASK         0 x3ff0 2360         CORE3 WIN4 MASK           0 x3ff0 2268         CORE2 WIN5 MASK         0 x3ff0 2368         CORE3 WIN5 MASK           0 x3ff0 2270         CORE2 WIN6 MASK         0 x3ff0 2370         CORE3 WIN6 MASK           0 x3ff0 2270         CORE2 WIN7 MASK         0 x3ff0 2378         CORE3 WIN6 MASK           0 x3ff0 2280         CORE2 WIN6 MMAP         0 x3ff0 2380         CORE3 WIN7 MASK           0 x3ff0 2280         CORE2 WIN0 MMAP         0 x3ff0 2388         CORE3 WIN0 MMAP           0 x3ff0 2288         CORE2 WIN7 MMAP         0 x3ff0 2388         CORE3 WIN4 MAP           0 x3ff0 2299         CORE2 WIN3 MMAP         0 x3ff0 2398         CORE3 WIN4 MAP           0 x3ff0 2290         CORE2 WIN6 MMAP         0 x3ff0 2388         CORE3 WIN4 MAP                                                                                                                                      | 0 x3ff0_2228 | CORE2_WIN5_BASE   | 0 x3ff0_2328 | CORE3_WIN5_BASE   |

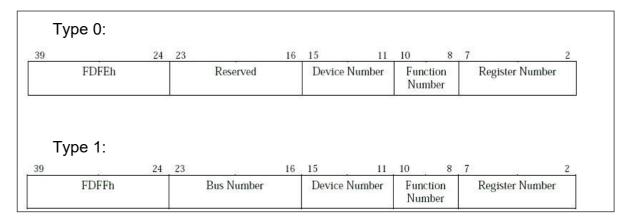

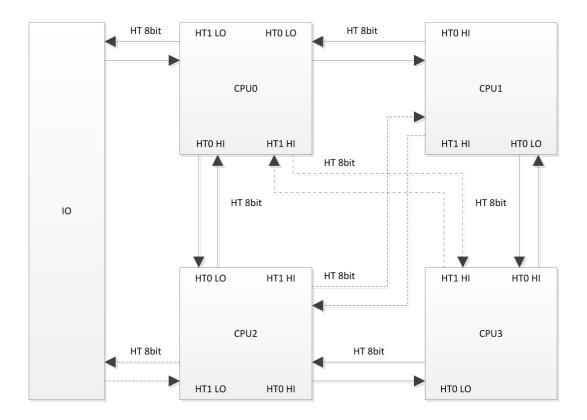

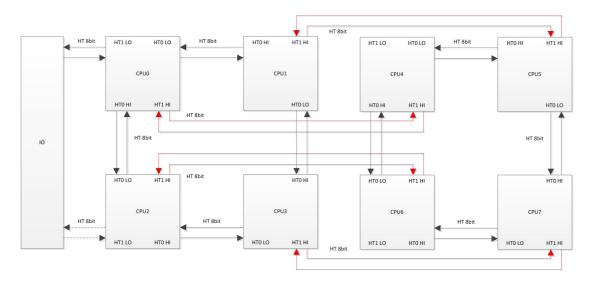

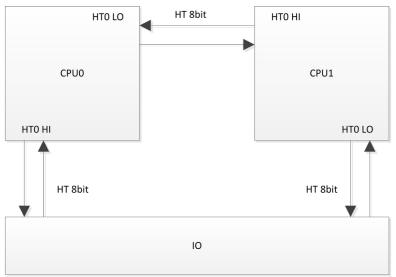

| 0 x3ff0 2240         CORE2 WIN0 MASK         0 x3ff0 2340         CORE3 WIN0 MASK           0 x3ff0 2248         CORE2 WIN1 MASK         0 x3ff0 2348         CORE3 WIN1 MASK           0 x3ff0 2250         CORE2 WIN2 MASK         0 x3ff0 2350         CORE3 WIN2 MASK           0 x3ff0 2258         CORE2 WIN3 MASK         0 x3ff0 2358         CORE3 WIN3 MASK           0 x3ff0 2260         CORE2 WIN4 MASK         0 x3ff0 2360         CORE3 WIN4 MASK           0 x3ff0 2268         CORE2 WIN5 MASK         0 x3ff0 2368         CORE3 WIN5 MASK           0 x3ff0 2270         CORE2 WIN6 MASK         0 x3ff0 2370         CORE3 WIN6 MASK           0 x3ff0 2278         CORE2 WIN7 MASK         0 x3ff0 2378         CORE3 WIN7 MASK           0 x3ff0 2280         CORE2 WIN0 MMAP         0 x3ff0 2380         CORE3 WIN1 MMAP           0 x3ff0 2288         CORE2 WIN1 MMAP         0 x3ff0 2380         CORE3 WIN1 MMAP           0 x3ff0 2290         CORE2 WIN3 MMAP         0 x3ff0 2398         CORE3 WIN3 MMAP           0 x3ff0 2298         CORE2 WIN3 MMAP         0 x3ff0 2398         CORE3 WIN4 MMAP           0 x3ff0 22a0         CORE2 WIN5 MMAP         0 x3ff0 23a0         CORE3 WIN4 MMAP           0 x3ff0 22a8         CORE2 WIN5 MMAP         0 x3ff0 23a8         CORE3 WIN4 MMAP                                                                                                                                   | 0 x3ff0_2230 | CORE2_WIN6_BASE   | 0 x3ff0_2330 | CORE3_WIN6_BASE   |