## **LOONGSON**

# Loongson 3A3000/3B3000 processor user manual

Part ii

GS464E processor core V1.2

In December 2017

Loongson Zhongke Technology Co. LTD

#### Copyright statement

The copyright of this document belongs to Loongson Technology Co., LTD., and all rights are reserved. No company or individual may publish, reprint or otherwise distribute any part of this document to third parties without written permission. Otherwise, it will be investigated for legal responsibility.

#### disclaimer

This document only provides phased information. The contents can be updated according to the actual situation of the product at any time without prior notice. The Company shall not be liable for any direct or indirect losses caused by improper use of documents.

#### Loongson Zhongke Technology Co. LTD

Loongson Technology Corporation Limited

Address: Loongson Industrial Park, Building No.2, Loongson Industrial Park, Zhongguancun Environmental Protection Technology Demonstration Park, Haidian District, Beijing

Zhongguancun Environmental Protection Park, Haidian District, Beijing

Tel: 010-62546668 Fax: 010-62600826

#### Reading guide

The User manual of Loongson 3A3000/3B3000 processor is divided into the first and the second volumes.

The second volume of The User's Manual of The 3A300/3B3000 processor introduces in detail the GS464E high-performance processor core used by the 3A300/3B3000 processor from the perspective of system software developers.

#### Special format meaning introduction

- 1. When the description of a Field of CP0 control register is involved in this document, the format of reg. Field is adopted, in which Reg is the mnemonic of the control register and Field is the mnemonic of the Field to be described in the storage. For example, Ebase control register.

- 2. The description of data content interception in this document is in the format of [m:n] or, indicating that the NTH bit to m of the content to be intercepted is selected m.n position M, n starts at 0, m is greater than or equal to n.

### Version history

| Document update record | The document name: | Loongson 3A3000/3B3000 processor<br>user manual<br>- part ii |  |  |  |

|------------------------|--------------------|--------------------------------------------------------------|--|--|--|

|                        | The version number | V1.2                                                         |  |  |  |

|                        | The founders:      | Chip R&d Department                                          |  |  |  |

|                        | Date created:      | 2017-12-20                                                   |  |  |  |

## **Update history**

| The serial num ber | Updated<br>date | Update one             | The version numbe r | Update<br>the<br>content                                                                                                                                        |

|--------------------|-----------------|------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | 2017/04/07      | Chip R&d<br>Department | V1.0                | The first draft is complete.                                                                                                                                    |

| 2                  | 2017/11/29      | Chip R&d<br>Department | V1.1                | <ol> <li>Fixed an error in the instruction list in Chapter 2.</li> <li>Section 2.3.1 adds the list of "DSP instructions no longer supported by MIPS"</li> </ol> |

| 3                  | 2017/12/20      | Chip R&d Department    | V1.2                | Fixed 8 instructions in the instruction list in Chapter 2.                                                                                                      |

|                    |                 |                        |                     |                                                                                                                                                                 |

|                    |                 |                        |                     |                                                                                                                                                                 |

## Technical support

You can submit the problems of product use to our company through email or problem feedback website, and obtain technical support. After-sales Service

Email: service@loongson.cn

Question feedback web site: http://bugs.loongnix.org/

## directory

## 景目

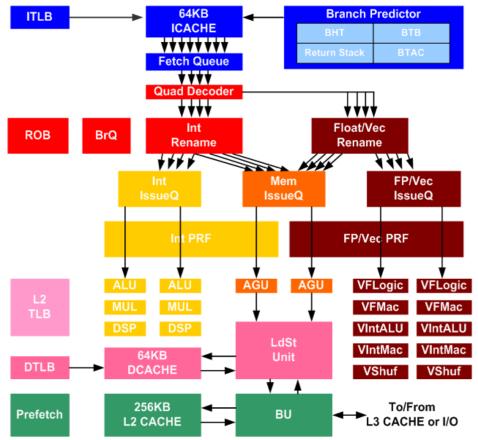

| 1 | Overview                                                  | w of processor core structure                                        | 1       |  |

|---|-----------------------------------------------------------|----------------------------------------------------------------------|---------|--|

|   | 1.1 Speed overview of processor core structure parameters |                                                                      |         |  |

| 2 | Instructi                                                 | on set Overview                                                      | · • • • |  |

|   | 2.1                                                       | MIPS64 compatible General instruction list                           | · • • • |  |

|   | 2.1.1                                                     | To fetch instruction                                                 | · • • • |  |

|   | 2.1.2                                                     | Operation instruction                                                | · • • • |  |

|   | 2.1.3                                                     | Jump and branch instructions                                         | · • • • |  |

|   | 2.1.4                                                     | Coprocessor 0 instruction                                            | 1       |  |

|   | 2.2                                                       | MIPS64 is compatible with floating point instruction set overview    | 1       |  |

|   | 2.2.1                                                     | FPU data type                                                        | 1       |  |

|   | 2.2.2                                                     | Floating point register                                              | 1       |  |

|   | 2.2.3                                                     | Floating point control register                                      | 1       |  |

|   | 2.2.4                                                     | Floating-point exception                                             | 1       |  |

|   | 2.2.5                                                     | MIPS64 is compatible with floating point instruction list            | 2       |  |

|   | 2.3                                                       | An overview of THE MIPS64 DSP instruction set                        | 2       |  |

|   | 2.3.1                                                     | MIPS64 DSP ASE compatible instruction list                           | 2       |  |

|   | 2.3.2                                                     | Supplementary instructions to MIPS DSP instruction manual            | 4       |  |

|   | 2.4                                                       | MIPS64 compatible instruction implementation definition              | 4       |  |

|   | 2.4.1                                                     | The load instruction that targets the no. 0 general purpose register | 4       |  |

|   | 2.4.2                                                     | PREF instruction                                                     | 4       |  |

|   | 2.4.3                                                     | RDHWR instruction                                                    | 4       |  |

|   | 2.4.4                                                     | PREFX instruction                                                    | 4       |  |

|   | 2.4.5                                                     | WAIT instruction                                                     | 4       |  |

|   | 2.4.6                                                     | SYNC instructions                                                    | 4       |  |

|   | 2.4.7                                                     | SYNCI instruction                                                    | 4       |  |

|   | 2.4.8                                                     | TLBINV and TLBINVF directives                                        | 4       |  |

|   | 2.4.9                                                     | CACHE directives                                                     | 5       |  |

|   | 2.4.10                                                    | Madd.fmt, Msub.fmt, Nmadd.fmt, Nmsub.fMT instruction                 | 5       |  |

|   | 2.4.11                                                    | EHB, SSNOP instructions                                              | 5       |  |

|   | 2.4.12                                                    | DI and EI instructions                                               | 5       |  |

|   | 2.5                                                       | Loong core expansion command set                                     | 5       |  |

| 3 | Processo                                                  | or running mode                                                      | 7       |  |

|   | 3.1                                                       | Processor run mode definition                                        | 7       |  |

|   | 3.1.1                                                     | Debug mode                                                           | 7       |  |

|   | 3.1.2                                                     | The root-core pattern                                                | 7       |  |

|   | 3.1.3                                                     | Root-user mode                                                       | 7       |  |

| 4 | Memory                                                    | management                                                           | 4       |  |

|   | 4.1                                                       | The basic concept                                                    | 4       |  |

|   | 4.1.1                                                     | Address space                                                        | 4       |  |

|   | 4.1.2                                                     | Segment and segment size (SEGBITS)                                   |         |  |

|   | 4.1.3                                                     | Physical Address size (PABITS)                                       |         |  |

|   | 4.1.4                                                     | Mapped Address and Unmapped Address                                  |         |  |

|   | 4.2                                                       | Host virtual address space                                           |         |  |

|   | 4.2.1                                                     | Host address space division and access control                       |         |  |

|   |                                                           | -                                                                    |         |  |

|   | 4.2.2  | The address translation, cacheability and cache consistency of host address space Kseg0 segment and Kseg1 segment      |    |

|---|--------|------------------------------------------------------------------------------------------------------------------------|----|

|   | 4.2.3  | The address translation and cacheability of the host address space Xkphys segment are consistent with the caproperties |    |

|   | 4.2.4  | Address translation of the kusEG segment of the host address space when status.erl =1                                  |    |

|   | 4.2.5  | Special treatment of host address space kseg3 when debug.dm =1                                                         |    |

|   | 4.2.6  | Special handling of data access to virtual addresses when status.ux =0 in user mode                                    |    |

|   | 4.3    | TLB - based virtual and real address mapping                                                                           |    |

|   | 4.3.1  | TLB hierarchy.                                                                                                         |    |

|   | 4.3.2  | JTLB structure                                                                                                         |    |

|   | 4.3.3  | JTLB table item                                                                                                        |    |

|   | 4.3.4  | TLB software management                                                                                                |    |

|   | 4.3.5  | TLB initialization and clearing                                                                                        |    |

|   | 4.3.6  | TLB - based virtual address translation process                                                                        |    |

| 5 |        | ation and management of caches                                                                                         |    |

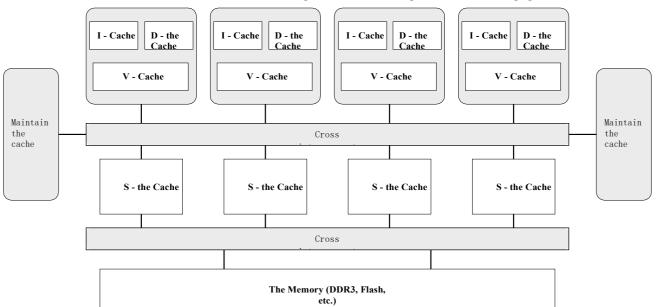

| 3 | 5.1    | Processor storage hierarchy and cache hierarchy                                                                        |    |

|   | 5.1.1  | Processor storage hierarchy and cache hierarchy                                                                        |    |

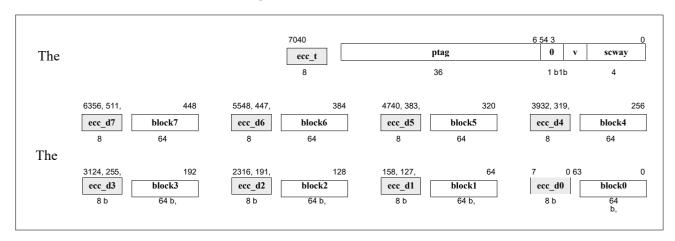

|   | 5.1.2  | Level 1 instruction Cache (I-cache)                                                                                    |    |

|   | 5.1.3  | Level 1 data Cache (D-Cache)                                                                                           |    |

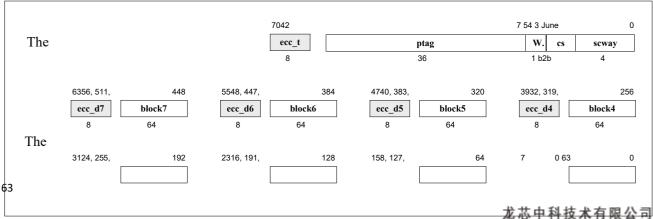

|   | 5.1.4  | Level 2 Sacrifice Cache (V-Cache)                                                                                      |    |

|   | 5.1.5  | Level 3 Shared Cache (V-Cache)                                                                                         |    |

|   | 5.1.5  | The cache algorithm has the same properties as the cache                                                               |    |

|   | 5.2.1  | Non-cache algorithm                                                                                                    |    |

|   | 5.2.1  | e e e e e e e e e e e e e e e e e e e                                                                                  |    |

|   | 5.2.3  | Consistent caching algorithm.                                                                                          |    |

|   |        | Non-cache acceleration algorithm                                                                                       |    |

|   | 5.3    | Cache management                                                                                                       |    |

|   | 5.4    | CACHE directives                                                                                                       |    |

|   | 5.4.1  |                                                                                                                        |    |

|   | 5.4.2  | Cache initialization                                                                                                   |    |

|   | 5.4.3  | Maintain consistency between level 1 instruction cache and level 1 data cache                                          |    |

|   | 5.4.4  | Maintain cache consistency between processor and DMA device                                                            |    |

| _ | 5.4.5  | Cache alias and page coloring                                                                                          |    |

| 6 |        | or exceptions and interrupts                                                                                           |    |

|   | 6.1    | Processor exception                                                                                                    |    |

|   | 6.1.1  | Exception priority                                                                                                     |    |

|   | 6.1.2  | Exception entry vector position                                                                                        |    |

|   | 6.1.3  | The processor hardware responds to the exception's generic processing                                                  |    |

|   | 6.1.4  | Cold reset exception.                                                                                                  |    |

|   | 6.1.5  | Non-masking interrupt                                                                                                  |    |

|   | 6.1.6  | Interrupt exception                                                                                                    |    |

|   | 6.1.7  | Wrong address exception                                                                                                |    |

|   | 6.1.8  | TLB rewrites the exception.                                                                                            |    |

|   | 6.1.9  | XTLB rewrites the exception.                                                                                           |    |

|   | 6.1.10 | TLB is not an exception                                                                                                |    |

|   | 6.1.11 | TLB modification exceptions                                                                                            |    |

|   | 6.1.12 | TLB performs blocking exceptions                                                                                       |    |

|   | 6.1.13 | TLB reads prevent exceptions                                                                                           |    |

|   | 6.1.14 | Cache error exception                                                                                                  |    |

|   | 6.1.15 | Exception for integer overflow                                                                                         | 78 |

| ( | 6.1.16  | Trap exceptions                                                  | 78  |

|---|---------|------------------------------------------------------------------|-----|

| ( | 6.1.17  | System call exception                                            | 78  |

| ( | 6.1.18  | Breakpoint exception                                             | 78  |

| ( | 6.1.19  | Reservation instruction exception                                | 79  |

| ( | 6.1.20  | No exceptions can be made to the coprocessor                     | 80  |

| ( | 6.1.21  | Floating-point exception                                         | 80  |

| ( | 6.1.22  | Floating point stack exception                                   | 80  |

| ( | 6.2     | interrupt                                                        | 80  |

| ( | 6.2.1   | Requirements for interrupt response                              | 80  |

| ( | 6.2.2   | Interrupt mode                                                   | 80  |

| ( | 6.2.3   | Additional notes on interrupt handling                           | 84  |

| 7 | Coproce | essor register 0                                                 | 86  |

| 7 | 7.1     | Root coprocessor 0 register overview                             | 86  |

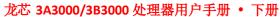

| - | 7.2     | Index Register (CP0 Register 0, Select 0)                        | 85  |

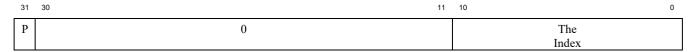

| - | 7.3     | Random Register (CP0 Register 1, Select 0)                       | 86  |

| 7 | 7.4     | EntryLo0 and EntryLo1 registers (CP0 Register 2 and 3, Select 0) |     |

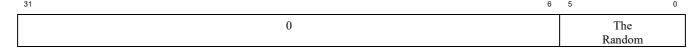

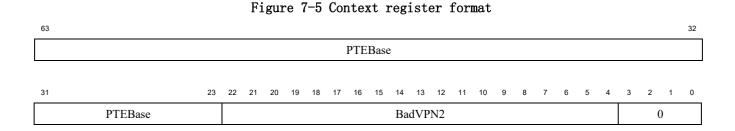

| 7 | 7.5     | Context Register (CP0 Register 4, Select 0)                      |     |

| 7 | 7.6     | UserLocal Register (CP0 Register 4, Selelct 2)                   |     |

| 7 | 7.7     | PageMask Register (CP0 Register 5, Select 0)                     | 92  |

| - | 7.8     | PageGrain Register (CP0 Register 5, Select 1)                    | 94  |

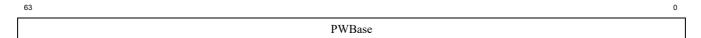

| 7 | 7.9     | PWBase Register (CP0 Register 5, Select 5)                       |     |

| 7 | 7.10    | PWField Register (CP0 Register 5, Select 6)                      | 98  |

| - | 7.11    | PWSize Register 5, Select 6                                      | 100 |

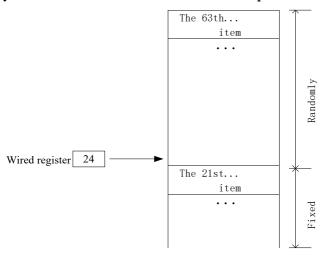

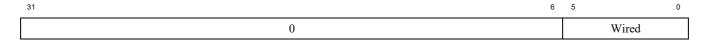

| 7 | 7.12    | Wired Register (CP0 Register 6, Select 0)                        | 102 |

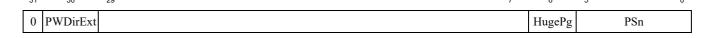

| 7 | 7.13    | PWCtl Register 6, Select 6                                       | 103 |

|   | 7.14    | Trade characters for a Register (CP0 Register 7, Select 0)       | 104 |

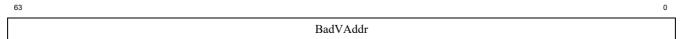

| - | 7.15    | BadVAddr Register (CP0 Register 8, Select 0)                     | 105 |

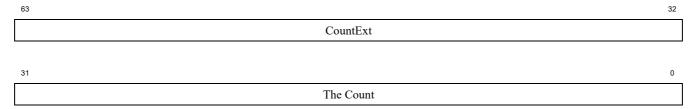

| - | 7.16    | Count Register 9, Select 0                                       | 106 |

| 7 | 7.17    | GSEBase Register (CP0 Register 9, Select 6)                      | 107 |

| 7 | 7.18    | PGD Register (CP0 Register 9, Select 7)                          | 108 |

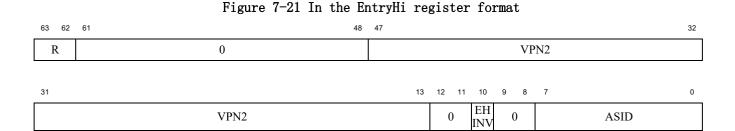

| 7 | 7.19    | EntryHi Register (CP0 Register 10, Select 0)                     | 109 |

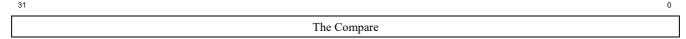

| 7 | 7.20    | Compare Register (CP0 Register 11, Select 0)                     | 106 |

| 7 | 7.21    | Status Register (CP0 Register 12, Select 0)                      | 107 |

| 7 | 7.22    | IntCtl Register (CP0 Register 12, Select 1)                      | 109 |

| 7 | 7.23    | SRSCtl Register (CP0 Register 12, Select 2)                      | 110 |

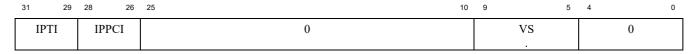

| 7 | 7.24    | Cause Register (CP0 Register 13, Select 0)                       | 111 |

| 7 | 7.25    | EPC Register (CP0 Register 14, Select 0)                         | 113 |

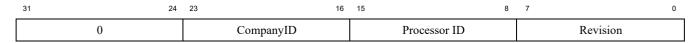

| 7 | 7.26    | PRId Register (CP0 Register 15, Select 0)                        | 114 |

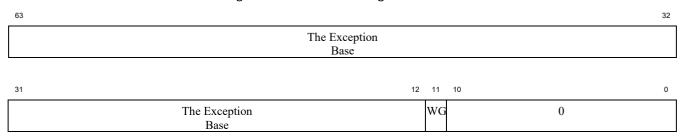

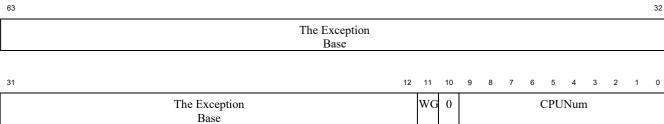

| 7 | 7.27    | EBase Register (CP0 Register 15, Select 1)                       | 115 |

| 7 | 7.28    | Config Register (CP0 Register 16, Select 0)                      | 116 |

| 7 | 7.29    | Config1 Register (CP0 Register 16, Select 1)                     | 117 |

| 7 | 7.30    | Config2 Register (CP0 Register 16, Select 2)                     | 118 |

| 7 | 7.31    | Config3 Register (CP0 Register 16, Select 3)                     | 119 |

| 7 | 7.32    | Config4 Register (CP0 Register 16, Select 4)                     | 121 |

| 7 | 7.33    | Config5 Register (CP0 Register 16, Select 5)                     | 123 |

| 7 | 7.34    | GSConfig Register (CP0 Register 16, Select 6)                    | 124 |

| 7 | 7.35    | LLAddr Register (CP0 Register 17, Select 0)                      | 127 |

| 7 | 7.36    | XContext Register (CP0 Register 20, Select 0)                    | 128 |

|   | 7.37    | Diag Register (CP0 Register 22, Select 0)                        | 130 |

|   | 7.38     | GSCause Register (CP0 Register 22, Select 1)           | 131 |

|---|----------|--------------------------------------------------------|-----|

|   | 7.39     | VPID Register (CP0 Register 22, Select 2)              | 132 |

|   | 7.40     | Debug Register (CP0 Register 23, Select 0)             | 133 |

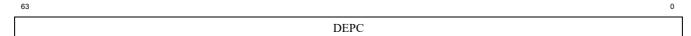

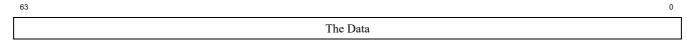

|   | 7.41     | DEPC Register (CP0 Register 24, Select 0)              | 134 |

|   | 7.42     | PerfCnt Register (CP0 Register 25, Select 0~7)         | 135 |

|   | 7.43     | ErrCtl Register (CP0 Register 26, Select 0)            | 137 |

|   | 7.44     | CacheErr Register (CP0 Register 27, Select 0)          | 138 |

|   | 7.45     | CacheErr1 Register (CP0 Register 27, Select 1)         | 140 |

|   | 7.46     | TagLo register (CP0 Register28, Select 0)              | 141 |

|   | 7.47     | DataLo Register (CP0 Register 28, Select 1)            | 144 |

|   | 7.48     | TagHi Register (CP0 Register 29, Select 0)             | 145 |

|   | 7.49     | DataHi Register (CP0 Register 29, Select 1)            | 146 |

|   | 7.50     | ErrorEPC Register (CP0 Register 30, Select 0)          | 147 |

|   | 7.51     | DESAVE Register (CP0 Register 31, Select 0)            | 148 |

|   | 7.52     | KScratch1~6 registers (CP0 Register 31, Select 2~7)    | 149 |

| 8 | Analysis | s and optimization of processor performance            | 150 |

|   | 8.1      | Organization and access method of performance counters | 150 |

|   | 8.1.1    | Processor core performance counter                     | 150 |

|   | 8.1.2    | Shared cache performance counters                      | 150 |

|   | 8.2      | Processor performance count events                     | 151 |

|   | 8.2.1    | Processor core performance count event definition      | 151 |

|   | 8.2.2    | Shared cache performance count event definition        |     |

|   |          |                                                        |     |

## Figure directory

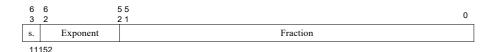

| Figure 2-1 FPU floating point data format 11                                                        |

|-----------------------------------------------------------------------------------------------------|

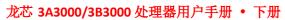

| Figure 2-2 FPU fixed-point data format 13                                                           |

| Figure 2-3 FIR register format 13                                                                   |

| Figure 2-4. FCSR register format 14                                                                 |

| Figure 2-5 FCCR register format 15                                                                  |

| Figure 2-6 FEXR register format 16                                                                  |

| Figure 2-7 FENR register format 16                                                                  |

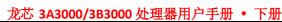

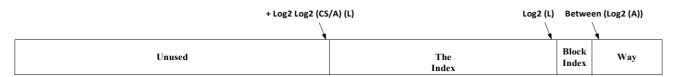

| Figure 2-8. Address resolution format of the Index class CACHE instruction 34                       |

| Figure 4-1 Xkphys segment virtual address resolution method 49                                      |

| Figure 5-1 Longson 3A3000 chip processor storage level 59                                           |

| Figure 5-2. Structure of level 1 instruction cache line is 60                                       |

| Figure 5-3 The row structure of the first-level data cache is 61                                    |

| Figure 5-4 Shows the second-level sacrifice cache row structure for 62                              |

| Figure 5-5 Shows the three-level Shared cache row structure for 64                                  |

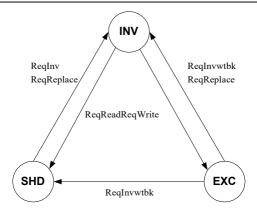

| Figure 5-6 Cache state transition under conformance protocol 65                                     |

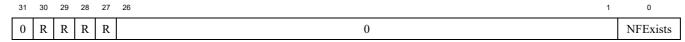

| Figure 7-1. Index register format 85                                                                |

| Figure 7-2. Random register format 86                                                               |

| Figure 7-3 Register format 87 for THE DMFCO/DMTCO instruction access for EntryLoO and EntryLo1      |

| Figure 7-4 Register format 88 for EntryLoO and EntryLo1 when accessed by the MFCO/MTCO instructions |

|                                                                                                     |

| Figure 7-5 Context register format 90                                                               |

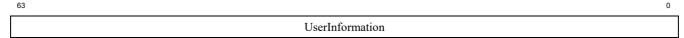

| Figure 7-6 UserLocal register format 91                                                             |

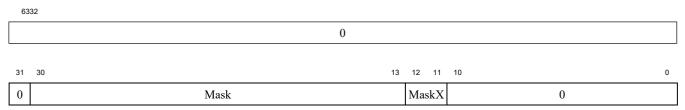

| Figure 7-7 PageMask register format 92                                                              |

| Figure 7-8 PageGrain register format 93                                                             |

| Figure 7-9 Page table access process 94 supported by PWBase, PWField, PWSize and PWCtl .            |

| Figure 7-10. PWBase register format 94                                                              |

| Figure 7-11. PWField register format 95                                                             |

| Figure 7-12. PWSize register format 96                                                              |

| Figure 7-13 Fixed table entry and random replacement table entry boundary in VTLB 97 .              |

| Figure 7-14 Wired register format 97                                                                |

| Figure 7-15 PWCtl register format 98                                                                |

| Figure 7-16 For trade A register format 99                                                          |

| Figure 7-17 BadVAddr register format 100                                                            |

| Figure 7-18. Count register format 101                                                              |

| Figure 7-19 GSEBase register format 102                                                             |

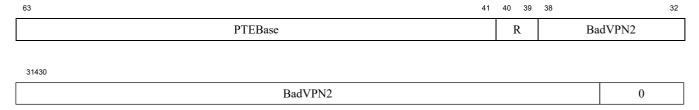

| Figure 7-20 PGD register format 103                                                                 |

| Figure 7-21. EntryHi register format 104                                                            |

| Figure 7-22 Compare register format 106                                                             |

| Figure 7-23 Status register format 107                                                              |

| Figure 7-24 IntCtl register format 109                                                              |

| Figure 7-25 SRSCtl register format 110                                                              |

| Figure 7-26 Cause register format 111                                                               |

Figure 7-27 EPC register format 113 .....

| Figure 7-28 PRId register format 114                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------|

| Figure 7-29 EBase register format 115                                                                                     |

| Figure 7-30. Config register format 116                                                                                   |

| Figure 7-31 Config1 register format 117                                                                                   |

| Figure 7-32 Config2 register format 118                                                                                   |

| Figure 7-33 Config3 register format 119                                                                                   |

| Figure 7-34 Config4 register format 121                                                                                   |

| Figure 7-35. Config5 register format 123                                                                                  |

| Figure 7-36 GSConfig register format 124                                                                                  |

| Figure 7-37. LLAddr register format 127                                                                                   |

| Figure 7-38 XContext register format 128                                                                                  |

| Figure 7-39 Diag register format 129                                                                                      |

| Figure 7-40 GSCause register format 131                                                                                   |

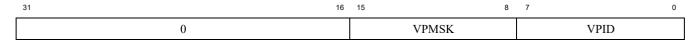

| Figure 7-41 VPID register format 132                                                                                      |

| Figure 7-42 DEPC register format 134                                                                                      |

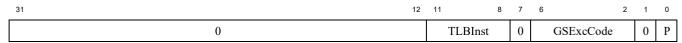

| Figure 7-43 PerfCnt Control register format 135                                                                           |

| Figure 7-44 PerfCnt Counter register format 136                                                                           |

| Figure 7-45 ErrCtl register format 137                                                                                    |

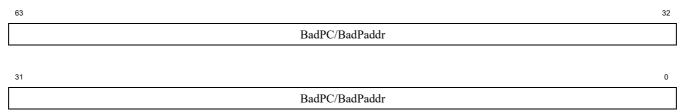

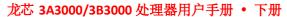

| Figure 7-46 CacheErr register format 138 when used for I-Cache error-checking information                                 |

| Figure 7-47 CacheErr register format 138 when used for D-Cache error-checking information                                 |

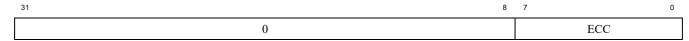

| Figure 7-48 CacheErrl register format 140                                                                                 |

| Figure 7-49 The TagLo register is used to access the I-Cache Tag in format 141                                            |

| Figure 7-50 TagLo register is used for format 141 when accessing the D-Cache Tag                                          |

| Figure 7-51 TagLo register in format 142 for accessing the V-Cache Tag                                                    |

| Figure 7-52 The TagLo register is used to access the S-Cache Tag in format 142                                            |

| Figure 7-53. The TagLo register is in format 143 for accessing each level of Cache Data                                   |

| Figure 7-54 The DataLo register is used for i-Cache access in format 144                                                  |

| Figure 7-55 Shows the format 145 of the TagHi register used to access the various Cache tags $\left( \frac{1}{2} \right)$ |

| Figure 7-56 The TagHi register is in format 145 for accessing each level of Cache Data .                                  |

| Figure 7-57 DataHi registers are used for i-Cache access in format 146                                                    |

| Figure 7-58. ErrorEPC register format 147                                                                                 |

| Figure 7-59 DESAVE register format 148                                                                                    |

| Figure 7-60 KScratchn register format 149                                                                                 |

## The table directory

| Table 2-1 CPU instruction set: access instruction 5                                   |

|---------------------------------------------------------------------------------------|

| Table 2-2 Operation instruction: arithmetic instruction (ALU immediate number) 6      |

| Table 2-3 Operation instruction: arithmetic instruction (3 operands) 6                |

| Table 2-4 Operation instruction: arithmetic instruction (2 operands) 7                |

| Table 2-5 Operation instruction: multiplication and division instruction 7            |

| Table 2-6 Operation instruction: shift instruction 7                                  |

| Table 2-7 Jump and branch instructions 8                                              |

| Table 2-8 Coprocessor instruction 0 9                                                 |

| Table 2-9 Other instructions: Special instruction 10                                  |

| Table 2-10 Other instructions: Exceptions fall into instruction 10                    |

| Table 2-11 Other instructions: Conditional move instruction 10                        |

| Table 2-12 Other instructions: Prefetch instruction 10                                |

| Table 2-13 Floating point format related parameters 12                                |

| Table 2-14 Calculation method of floating point value V 12                            |

| Table 2-15 Maximum and minimum values of floating point Numbers 12                    |

| Table 2-16 FIR register fields describe 13                                            |

| Table 2-17 Describes the FCSR register field 14                                       |

| Table 2-18 Codes for rounding mode (RM) 15                                            |

| Table 2-19 Default handling for floating point exceptions: 17                         |

| Table 2-20 Float branch jump instructions 19                                          |

| Table 2-21 Floating point operation instructions 19                                   |

| Table 2-22 Floating-point branch jump instruction 20                                  |

| Table 2-23 Floating-point branch jump instruction 20                                  |

| Table 2-24 Floating-point branch jump instruction 20                                  |

| Table 2-25 Floating-point branch jump instruction 21                                  |

| Table 2-26 CACHE instruction OP [1:0] corresponds to the CACHE hierarchy 34           |

| Table 2-27 Instruction of longson extended access class 35                            |

| Table 2-28 Instructions for extended arithmetic and logic operations of the Godson 37 |

| Table 2-29 Longson extension X86 binary translation acceleration instruction 38       |

| Table 2-30 Acceleration instruction of ARM BINARY translation extension               |

| Table 2-31 Loong core extension 64 bit multimedia instruction 42                      |

| Table 2-32 Godson expansion miscellaneous instruction 44                              |

| Table 3-1 Processor mode determination is based on 45                                 |

| Table 4-1 Host address space division and access control                              |

| Table 4-2 TLB management related CPO register 52                                      |

| Table 4-3 TLB manages related privileges instruction 52                               |

| Table 5-1 Cache parameter 60                                                          |

| Table 5-2 Tertiary Shared cache body selection bit and index address 63               |

| Table 5-3 CACHE instruction 66 in root mode                                           |

| Table 6-1 Exception priority 71                                                       |

| Table 6-2 Exception vector base address 72                                            |

| Table 6-3 Exception vector offset 72                                                  |

|                                                                                       |

| Table 6-4 Each interrupt request generates 81 in compatible interrupt mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 6-5 Priority relationship among interrupts in vector interrupt mode 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Table 6-6 Interrupt mode decision 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 7-1 List of coprocessor zero registers 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Table 7-2 Index register field description 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table 7-3 Description of Random register field 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 7-4 The register fields for EntryLoO and EntryLo1 are described as 87 for DMFCO/DMTCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| instruction access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table 7-5 The register fields for EntryLo0 and EntryLo1 at the time of MFCO/MTCO instruction access the substitution of the substitution of the substitution access to the substitution of the substitution of the substitution access to the substitution access to the substitution of the substitution access to the s |

| are described as 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 7-6 Cache attribute encoding Table 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Table 7-7 Context register fields describe 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table 7-8 UserLocal register field description 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 7-9 PageMask register field description 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table 7-10 Mask domain codes and page sizes 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Table 7-11 The PageGrain register field is described in 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Table 7-12 PWBase register fields describe 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table 7-13 PWField register fields describe 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

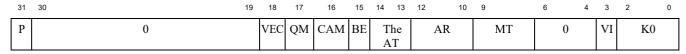

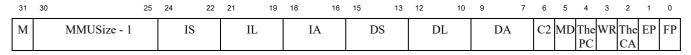

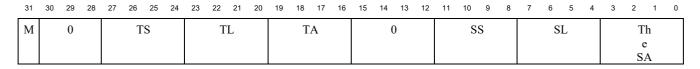

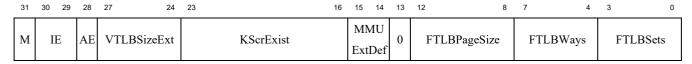

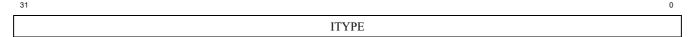

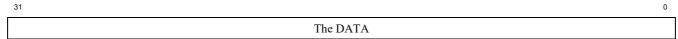

| Table 7-14 PWSize register fields describe 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |